# This Page Is Inserted by IFW Operations and is not a part of the Official Record

## **BEST AVAILABLE IMAGES**

Defective images within this document are accurate representations of the original documents submitted by the applicant.

Defects in the images may include (but are not limited to):

- BLACK BORDERS

- TEXT CUT OFF AT TOP, BOTTOM OR SIDES

- FADED TEXT

- ILLEGIBLE TEXT

- SKEWED/SLANTED IMAGES

- COLORED PHOTOS

- BLACK OR VERY BLACK AND WHITE DARK PHOTOS

- GRAY SCALE DOCUMENTS

# IMAGES ARE BEST AVAILABLE COPY.

As rescanning documents will not correct images, please do not report the images to the Image Problem Mailbox.

### PATENT ABSTRACTS OF JAPAN

(11)Publication number:

11-219146

(43) Date of publication of application: 10.08.1999

(51)Int.CI.

G09F 9/00 G09F 9/33 H01L 33/00

(21)Application number: 10-311569

(71)Applicant: MITSUBISHI CHEMICAL CORP

SARNOFF CORP

(22)Date of filing:

28.09.1998

(72)Inventor: KANE MICHAEL GILLIS

ATHERTON JAMES HAROLD STEWART ROGER GREEN **CUOMO FRANK PAUL**

(30)Priority

Priority number: 97 60386

Priority date : 29.09.1997

Priority country: US

97 60387

29.09.1997

US

#### (54) ACTIVE MATRIX LIGHT EMITTING DIODE PICTURE ELEMENT STRUCTURE AND **METHOD**

#### (57)Abstract:

PROBLEM TO BE SOLVED: To reduce uneveness of a current in a light emitting diode(LED) so as to improve uniformity of luminance by composing picture element structure of NMOS transistors, a capacitor and the LED.

SOLUTION: Picture element structure 300 is composed of five NMOS transistors 310-350, a capacitor 302 and an LED 304. A selection line 370 is connected to a gate of the transistor 350, and a data line 360 is connected to one terminal of the capacitor 302. An auto-zero line 380 is connected to a gate of the transistor 340, and a VDD line 390 is connected to the drains of the transistors 320, 220. One terminal of the capacitor 302 is connected to the source of the transistor 330 and the drains of the transistors 340, 350, and the sources of the transistors 310. 320 are connected to one terminal of the LED 304. With this constitution, unevenness of a current can be reduced in the LED 304.

#### **LEGAL STATUS**

[Date of request for examination]

[Date of sending the examiner's decision of

rejection]

[Kind of final disposal of application other than the examiner's decision of rejection or application converted registration]

[Date of final disposal for application]

[Patent number]

[Date of registration]

[Number of appeal against examiner's decision of rejection]

[Date of requesting appeal against examiner's decision of rejection]

[Date of extinction of right]

Copyright (C); 1998,2000 Japan Patent Office

### (12) 公開特許公報(A)

(11)特許出願公開番号

### 特開平11-219146

(43)公開日 平成11年(1999)8月10日

| (51) Int.Cl. <sup>6</sup> | 識別記号              |        | FΙ      |              |                     |        |

|---------------------------|-------------------|--------|---------|--------------|---------------------|--------|

| G 0 9 G 3/14              |                   |        | G 0.9 G | 3/14         | J                   |        |

| G09F 9/00                 | 3 3 7             |        | G09F    | 9/00         | 337B                |        |

| 9/33                      |                   |        |         | 9/33         | Z                   |        |

|                           |                   |        |         | •            | М                   |        |

| H01L 33/00                |                   |        | H01L    | 33/00        | L                   |        |

|                           | 審査請求              | 未請求 請求 |         | L 外国語出願      | (全 80 頁)            | 最終頁に続く |

| (21)出願番号                  | 特願平10-311569      |        | (71)出顧人 |              |                     |        |

| (22)出願日                   | 平成10年(1998) 9月28日 |        |         |              | 会社<br>区丸の内二丁        | 目5番2号  |

| (31)優先権主張番号               | 60/060, 386       |        | (71)出願人 |              | ーポレーション             | ·      |

| (32)優先日                   | 1997年 9 月29日      |        |         | アメリカ合衆       | 国、ニュージ・             | ャージー州・ |

| (33)優先権主張国                | 米国 (US)           |        |         | 08543-5300、  | プリンストン              | CN5300 |

| (31)優先権主張番号               | 6.0/060, 387      |        |         | ワシントン        | ロード 201             |        |

| (32) 優先日                  | 1997年9月29日        |        | (72)発明者 | ミカエル ギリス ケーン |                     |        |

| (33)優先権主張国                | 米国 (US)           |        |         | アメリカ合衆       | 国、ニュージ <del>・</del> | ャージー州・ |

|                           |                   |        |         | 08558、スキル    | マン、ロビン              | ドライブ   |

|                           |                   |        |         | 44           |                     |        |

|                           |                   |        | (74)代理人 | 弁理士 阿田       | 数彦                  |        |

|                           | ·                 |        |         |              |                     | 最終頁に続く |

#### (54) 【発明の名称】 アクティブマトリックス発光ダイオード画素構造およびその方法

#### (57)【要約】

【課題】画素構造の発光ダイオードにおける電流の不均一性を低減することによって、輝度の不均一性を改善するLED画素構造と方法とを提供する。

【解決手段】少なくとも一つの画素を備えるディスプレイであって、上記画素は、第1トランジスタと、キャパシタと、第2トランジスタと、第3トランジスタと、第4トランジスタと、第5トランジスタと、光要素とから成り、それらの構成要素を特定に接続することにより構成されていることを特徴とするディスプレイ。

【請求項1】 少なくとも一つの画素を備えるディスプレイであって、当該画素は、(1)第1選択ラインへの接続用であるゲートと、ソースと、ドレインとを有する第1トランジスタと、(2)当該第1トランジスタのドレインが接続されている第1端子と、第2端子とを有するキャパシタと(3)オートゼロラインへの接続用であるゲートと、ソースと、当該第1トランジスタの当該ドレインが接続されているドレインとを有する第2トランジスタと、(4)第2選択ラインへの接続用であるゲー 10トと、当該第2トランジスタのドレインに接続されたソースと、ドレインとを有する第3トランジスタと、

1

- (5) 当該第1トランジスタのソースに接続されたゲートと、ソースと、当該第2トランジスタの当該ソースに 接続されたドレインとを有する第4トランジスタと、

- (6) 当該第1トランジスタのソースに接続されたゲートと、ソースと、当該第3トランジスタの当該ドレインに接続されたドレインとを有する第5トランジスタと、

- (7) 当該第4トランジスタのソースと当該第5トランジスタのソースとが、一方の端子に接続されている2個 20 の端子を有する光要素とから成ることを特徴とするディスプレイ。

【請求項2】 前記光要素が有機発光ダイオード (OLED) である請求項1に記載のディスプレイ。

【請求項3】 前記各トランジスタが非晶質シリコンから造られた薄膜トランジスタである請求項1又は2に記載のディスプレイ。

【請求項4】 前記第2選択ラインが前行からのオートゼロラインである請求項 $1\sim3$ の何れかに記載のディスプレイ。

【請求項5】 少なくとも一つの画素を備えたディスプ レイであって、当該画素は、(1)一つの選択ラインへ の接続用であるゲートと、ソースと、ドレインとを有す る第1トランジスタと、(2) 当該第1トランジスタの ドレインが接続されている第1端子と、第2端子とを有 するキャパシタと、(3) オートゼロラインへの接続用 であるゲートと、ソースと、当該第1トランジスタの当 該ドレインが接続されているドレインとを有する第2ト ランジスタと、(4) 当該第2トランジスタのソースに 接続された第1端子と、点灯ラインへの接続用の第2端 40 子とを有するダイオードと、(5)第1トランジスタの ソースに接続されたゲートと、ソースと、当該ダイオー ドの第1端子に接続されたドレインとを有する第3トラ ンジスタと、(6) 当該第3トランジスタのソースが、 一方の端子に接続されている2個の端子を有する光要素 とから成ることを特徴とするディスプレイ。

【請求項6】 前記ダイオードがショットキダイオードである請求項5に記載のディスプレイ。

【請求項7】 少なくとも一つの画素を備えたディスプレイであって、当該画素は、(1)第1選択ラインへの 50

接続用であるゲートと、ソースと、ドレインとを有する第1トランジスタと、(2)当該第1トランジスタのドレインが接続されている第1端子と、第2端子とを有するキャパシタと、(3)オートゼロラインへの接続用であるゲートと、当該第1トランジスタの当該ソースが接続されているソースと、ドレインとを有する第2トランジスタと、(4)第2選択ラインへの接続用であるゲートと、当該第2トランジスタのドレインに接続されたソースと、ドレインとを有する第3トランジスタと、

- (5) 当該第1トランジスタのソースに接続されたゲートと、ソースと、当該第3トランジスタの上記ソースに接続されたドレインとを有する第4トランジスタと、

- (6) 当該第1トランジスタのソースに接続されたゲートと、ソースと、当該第3トランジスタの当該ドレインに接続されたドレインとを有する第5トランジスタと、

- (7) 当該第4トランジスタのソースと当該第5トランジスタのソースとが、一方の端子に接続されている2個の端子を有する光要素とから成ることを特徴とするディスプレイ。

0 【請求項8】 前記光要素が有機発光ダイオード(OLED)である請求項7に記載のディスプレイ。

【請求項9】 前記第2選択ラインが前行からのオートゼロラインである請求項7又は8に記載のディスプレイ。

【請求項10】 (1) 少なくとも一つのオートゼロ化画素構造と、(2) 当該オートゼロ化画素構造にオートゼロ化の実行を可能にするため、当該オートゼロ化画素構造に接続されたオートゼロラインと、(3) オートゼロ電圧の範囲を拡張するため、一つの電圧を当該オートゼロ化画素構造に運ぶように、当該オートゼロ化画素構造に接続された第2ラインとから成るディスプレイ。

【請求項11】 光要素への印加エネルギーを制御する 回路を含む少なくとも1個の画素を有するディスプレイ を点灯する方法であって、(a) 画素をオートゼロ化するステップと、(b) データライン経由でデータを当該 画素へロードするステップと、(c) 保存されたデータ に基づいて当該光要素を点灯するステップとから成ることを特徴とする方法。

【請求項12】 前記オートゼロ化ステップ(a)の前に前記画素をプリチャージするステップを更に含む請求項11に記載の方法。

【請求項13】 前記オートゼロ化ステップ(a)が基準ブラックレベルを印加するステップを含む請求項11 又は12に記載の方法。

【請求項14】 少なくとも1個の画素を有するディスプレイを点灯する方法であって、(a) 当該画素の画素パラメータを測定するステップと、(b) 測定された画素パラメータに基づいて入力画素データを調整するステップと、(c) 調整された入力画素データに基づいて当該画素を点灯するステップとから成ることを特徴とする

2

方法。

【請求項15】 前記測定ステップ(a)が前記画素に よって引き出された電流を外部的に測定する請求項14 に記載の方法。

【請求項16】 前記調整ステップ(b)が、電圧オフ セット (Voffset) パラメータを求めるため、前記測定 された画素パラメータを使用して前記画素データを補正 する請求項14又は15に記載の方法。

【請求項17】 前記調整ステップ(b)が、更に、ゲ イン係数(C)パラメータを求めるため、前記測定され 10 た画素パラメータを使用して前記画素データを補正する 請求項16に記載の方法。

【請求項18】 ディスプレイコントローラと当該ディ スプレイコントローラに接続されると供に複数の画素か ら成るディスプレイとから成るシステムであって、当該 各画素が、(1)第1選択ラインへの接続用ゲートと、 ソースと、およびドレインとから成る第1トランジスタ と、(2) 当該第1トランジスタの当該ドレインに接続 された第1端子と、第2端子とを有するキャパシタと、 (3) オートゼロラインへの接続用ゲートと、当該第1 20 トランジスタの当該ソースに接続されたソースと、ドレ インとを有する第2トランジスタと、(4)第2選択ラ インへの接続用ゲートと、当該第2トランジスタの当該 ドレインに接続されたソースと、ドレインとを有する第 3トランジスタと、(5) 当該第1トランジスタの当該 ソースに接続されたゲートと、ソースと、当該第3トラ ンジスタの当該ソースに接続されたドレインとを有する 第4トランジスタと、(6) 当該第1トランジスタの当 該ソースに接続されたゲートと、ソースと、当該第3ト ランジスタの当該ドレインに接続されたドレインとを有 30 する第5トランジスタと、(7)当該第4トランジスタ のソースと当該第5トランジスタのソースとが、一方の 端子に接続されている2個の端子を有する光要素とから 成ることを特徴とするシステム。

【請求項19】 (1) 画素の画素パラメータを測定す るための測定モジュールと、(2) 当該測定された画素 パラメータを保存するための記憶装置とを有するディス プレイコントローラと、(3) 当該保存された画素パラ メータに基づいて調整された入力画素データを表示する ため、当該ディスプレイコントローラに接続されたディ 40 スプレイとから成るシステム。

【請求項20】 前記測定モジュールが前記画素によっ て引き出される電流を測定するための電流検知回路を有 する請求項19に記載のシステム。

#### 【発明の詳細な説明】

[0001]

【発明の属する技術分野】本発明は、アクティブマトリ ックス発光ダイオード画素(ピクセル)構造に関する。 本発明は、詳しくは、画素構造の発光ダイオードにおい

素構造と、前記アクティブマトリックス発光ダイオード 画素構造の作動方法に関する。尚、本出願は1997年9月2 9日出願の米国仮出願第 60/060,386 号および1997年9月 29日出願の米国仮出願第 60/060,387 号の優先権を主張 すると供に、本出願に引用する。

[0002]

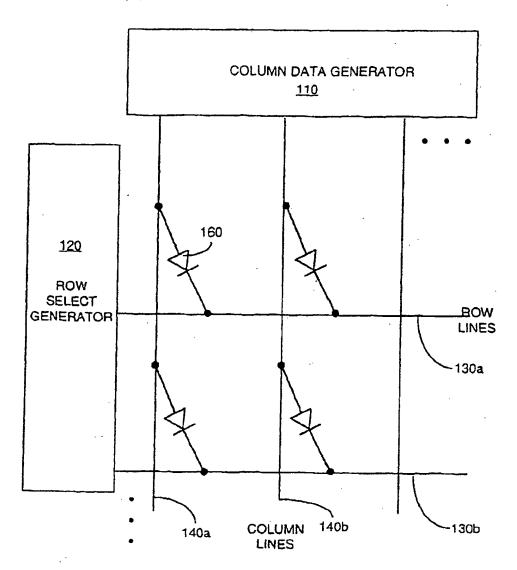

【従来の技術】図1に示すようなマトリックスアドレッ シングを使用して画素を点灯するマトリックスディスプ レイは、当該技術分野において周知である。典型的なデ ィスプレイ100は、行と列に構成された画面要素すな わち表示要素(ピクセル)160を有する。このディス プレイは、列データ発生装置110と行データ発生装置 120を内蔵している。作動にあたっては、各行は行ラ イン130を介して順次通電されるとともに、対応する 列ラインを使用して対応する画素が通電される。パツシ ブマトリックスディスプレイにおいては、各行の画素は 順次1個ずつ点灯されるが、アクティブマトリックスデ ィスプレイにおいては、各列の画素に順次データがロー ドされる。 すなわち、 パッシブマトリックスディスプレ イの各列は全フレーム時間のほんの一部分で「通電状態 である」に過ぎないが、アクティブマトリックスディス プレイの各列はフレーム時間の全体にわたって「通電状 熊とする」ことが出来る。

【0003】ポータブルディスプレイ、例えばラップト ップコンピュータの普及にともなって、さまざまなプレ イ技術、例えば液晶ディスプレイ(LCD)および発光 ダイオードディスプレイ (LED) が使用されるように なった。一般的に、ポータブルディスプレイにおいて は、ディスプレイを使用するポータブルシステムの電力 を節約し、それによってポータブルシステムの「使用時 間」を延長できる様にすることが重要である。

【0004】 LCDにおいては、ディスプレイの使用中 の全期間にわたってバックライトがオンになっている。 すなわち、LCD内のすべての画素が点灯され、ある画 素を「暗く」するには、画素を通る光を偏光層でさえぎ る。これに対して、LEDディスプレイは、通電された 画素のみが点灯され、暗い画素を点灯する必要をなくし て省電力を図っている。

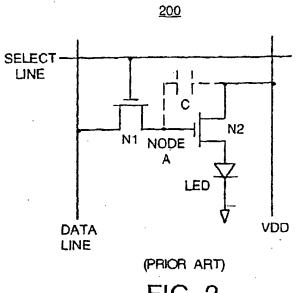

【0005】図2に、2個のNMOSトランジスタN1 とN2を有する従来技術のアクティブマトリックスLE D画素構造200を示す。この画素構造においては、ト ランジスタN1に通電することによりコンデンサCにデ ータ (電圧) が先ず保存され、次に「駆動トランジス タ」N2に通電してLEDを点灯する。画素構造200 を使用したディスプレイでも節電は可能であるが、この 画素構造では、いくつかの原因により不均一な輝度レベ ルを呈する。

【0006】第一に、LEDの輝度はそこを通る電流に 比例することが観測されている。使用中、「駆動トラン て電流の不均一性を低減して輝度の均一性を改善する画 50 ジスタ」N2の閾値電圧がドリフトするためLEDを通 る電流が変化する可能性がある。この電流の変化がディ スプレイの輝度の不均一性の一因となる。

【0007】第二に、ディスプレイの輝度の不均一性の もう一つの原因は、「駆動トランジスタ」N2の製造に おいて見いだすことが出来る。いくつかの場合に、「駆 動トランジスタ」N2は、トランジスタの初期閾値電圧 の均一性の確保が困難な材料で作られ、その結果、画素 ごとに変動する。

【0008】第三に、LEDの電気的パラメータも不均 一性を呈することがある。例えば、バイアス温度ストレ 10 ス条件下では、OLED(有機発光ダイオード)のター ンオン電圧の増加が予想される。

【0009】従って、画素構造の「駆動トランジスタ」 における閾値電圧の変動に起因する電流の不均一性を低 滅する画素構造と、それに関連する方法が当該技術分野 において必要となっている。

#### [0010]

【発明が解決しようとする課題】本発明は、画素構造の 発光ダイオードにおける電流の不均一性の低減によって 輝度の均一性を改善するLED (またはOLED) 画素 20 構造と方法を提供することを目的とする。

#### [0011]

【課題を解決するための手段】上記課題を解決するため に、本発明者らは鋭意検討した結果、5個のNMOSト ランジスタ、コンデンサ、およびLEDから成る画素構 造が上記課題を解決できることを見出し、本発明を完成 するに至った。

【0012】すなわち、本発明の第一の要旨は、少なく とも一つの画素を備えるディスプレイであって、当該画 素は、(1)第1選択ラインへの接続用であるゲート と、ソースと、ドレインとを有する第1トランジスタ と、(2) 当該第1トランジスタのドレインが接続され ている第1端子と、第2端子とを有するキャパシタと (3) オートゼロラインへの接続用であるゲートと、ソ ースと、当該第1トランジスタの当該ドレインが接続さ れているドレインとを有する第2トランジスタと、

(4) 第2選択ラインへの接続用であるゲートと、当該 第2トランジスタのドレインに接続されたソースと、ド レインとを有する第3トランジスタと、(5) 当該第1 トランジスタのソースに接続されたゲートと、ソース と、当該第2トランジスタの当該ソースに接続されたド レインとを有する第4トランジスタと、(6) 当該第1 トランジスタのソースに接続されたゲートと、ソース と、当該第3トランジスタの当該ドレインに接続された ドレインとを有する第5トランジスタと、(7) 当該第 4トランジスタのソースと当該第5トランジスタのソー スとが、一方の端子に接続されている2個の端子を有す る光要素とから成ることを特徴とするディスプレイに存 する。

構造は3個のトランジスタと1個のダイオードから成

【0014】第1の要旨の他の好ましい態様において、 画素構造は5個のトランジスタを有する異なる画素構造

【0015】第1の要旨の他の好ましい態様において、 画素構造はオートゼロ化電圧範囲を拡張する追加のライ ンを1本備える。

【0016】本発明の第2の要旨は、画素パラメータを 測定し、それを使用して入力画素データを調節する、一 つの外部測定モジュールと種々の測定方法に存する。 [0017]

【発明の実施の形態】以下、本発明を図面を使用して詳 しく説明する。尚、理解を容易にするため、各図に共通 の要素は可能な限り同一の符号を付した。

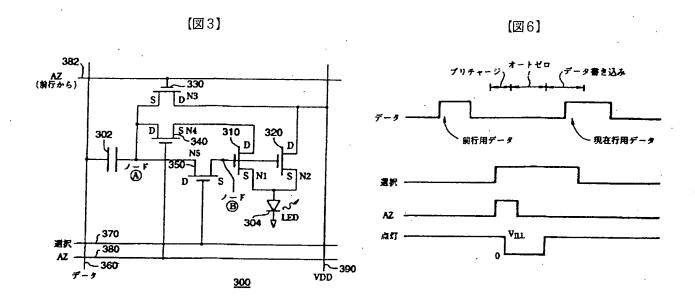

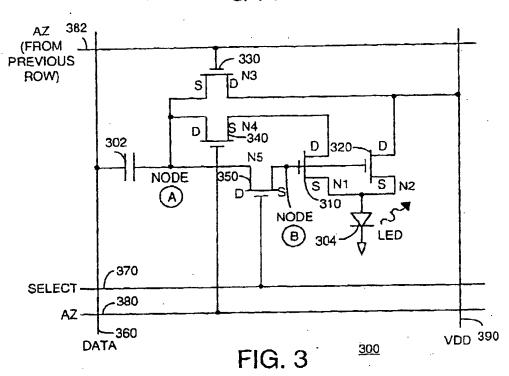

【0018】 図3は、本発明によるアクティブマトリッ クスLED画素構造300の略図である。好ましい実施 態様において、アクティブマトリックスLED画素構造 は、薄膜トランジスタ(TFT)、すなわちポリシリコ ンまたはアモルファスシリコンを使用して作られたトラ ンジスタを使用して実施される。同様に、好ましい実施 態様において、アクティブマトリックスLED画素構造 は、有機発光ダイオード(OLED)を使用する。この 画素構造は薄膜トランジスタと有機発光ダイオードを使 用して実施しているが、本発明は他のタイプのトランジ スタや発光ダイオードを使用しても実施できる。

【0019】この画素構造300は、トランジスタ閾値 電圧  $(V_t)$  の不均一性が大きくかつOLEDターンオ ン電圧の不均一性が大きい場合でも、均一な電流駆動を 30 提供する。すなわち、OLEDを通る電流を均一に保 ち、それによってディスプレイの輝度の均一性を確保す ることが望ましい。

[0020] 図3を参照すると、画素構造300は、5 個のNMOSトランジスタN1 (310)、N2 (32 0)、N3 (330)、N4 (340) およびN5 (3 50)、コンデンサ302、およびLED (OLED) (光要素) 304 (光要素) から成る。選択ライン37 0はトランジスタ350のゲートに接続されている。デ ータライン360はコンデンサ302の一方の端子に接 続されている。オートゼロライン380はトランジスタ 340のゲートに接続されている。VDDライン390 がトランジスタ320、330のドレインに接続されて いる。画素アレイ内の前の行からのオートゼロライン3 82が、トランジスタ330のゲートに接続されてい

【0021】前行からのオートゼロライン382は第2 の選択ラインとして実施可能であることに注目すべきで ある。すなわち、現在の画素のタイミングは、前行から のオートゼロライン382が第2の選択ラインを必要と 【0013】第1の要旨の好ましい態様において、画素 50 せずに利用でき、それによって現在の画素の複雑さとコ ストを低減するようになっている。

【0022】コンデンサ302の一つの端子は(ノード Aにおいて) トランジスタ330のソースと、トランジ スタ340、350のドレインに接続されている。トラ ンジスタ350のソースは (ノードBにおいて) トラン ジスタ310と320のゲートに接続されている。トラ ンジスタ310のドレインはトランジスタ340のソー スに接続されている。最後に、トランジスタ310と3 20のソースはLED304の一方の端子に接続されて いる。

【0023】前述のように、有機LEDディスプレイの 駆動には種々の不均一性による問題が多い。本発明は、 これらの問題を対象とする有機LEDディスプレイの構 造に関する。すなわち、各LED画素は、LEDターン オン電圧の変動やTFT閾値電圧の変動に鈍感な方法で 駆動される。すなわち、現在の画素は、LEDターンオ ン電圧やTFT閾値電圧の変動に対処するために使用さ れるオートゼロ化方法を使用して、オフセット電圧パラ メータを求めることが出来る。

【0024】更に、従来のアクティブマトリックス液晶 20 ディスプレイにおいて使用された方法に極めて類似する 方法によって、各画素にデータがデータ電圧として供給 される。その結果、本発明のディスプレイ構造は、従来 の行と列のスキャナに対し、外付けでも内蔵でも使用す ることが出来る。

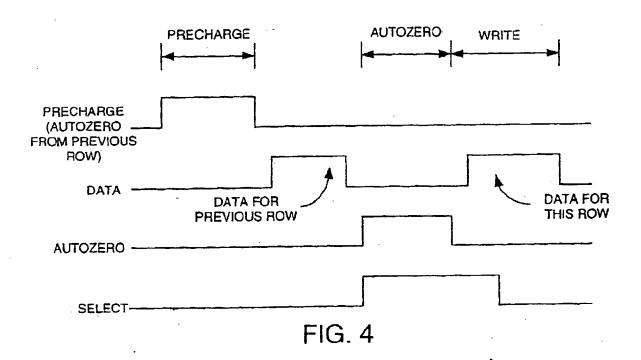

【0025】本発明の画素は、5個のTFTと、1個の コンデンサと、LEDとを使用する。TFTの接続は、 LEDのカソードにではなく、アノードに接続されるこ とに注目すべきであり、このことは従来の有機LEDに おいてはIT〇がホールエミッタであるという事実によ 30 って必要とされる。従って、LEDはTFTのドレイン にではなく、ソースに接続される。各ディスプレイの列 は、2本の行ライン(オートゼロラインと選択ライン) と、1-1/2列ライン(データラインと、隣の列と共 有する+VDDライン)を有する。各ライン上の波形も 図4に示す。画素300の作動を以下3フェーズ、すな わち3段階で詳述する。

【0026】第一フェーズはプリチャージフェーズであ る。前行382のオートゼロ(AZ)ライン上の正のパ ルスがトランジスタ330を「オン」にし、画素のノー 40 ドAをVad、例えば+10Vまでプリチャージする。次 、にデータラインが、前行の画素へデータを書き込むた め、そのベースライン値から変化し、そのベースライン・ へ戻る。これは考慮中の画素への正味効果を持たない。 【0027】第二フェーズはオートゼロフェーズであっ る。現在の行のAZラインとSELECTラインが高く なり、トランジスタ340、350を「オン」にし、ト ランジスタN1 310のゲートを落とし、ターンオン 電圧へと自己バイアスをかけ、LEDに極くわずかな電 流を流す。このフェーズにおいて、LEDのターンオン 50 デューティサイクルが極めて短く、認識できるほどには

電圧とN1の閾値電圧の合計がN1のゲートに保存され る。N1とN2とはごく接近して配置できるので、それ らの初期閾値電圧は極めて類似している。更に、これら 2個のトランジスタのソースに対するゲート電圧Vgs は 同じはずである。TFTの閾値電圧のドリフトはTFT の全寿命にわたってVgsのみに依存するので、これらデ バイスの閾値電圧はTFTの全寿命にわたって追従する と見なすことが出来る。従って、N2の閾値電圧もその ゲート上に保存される。オートゼロ化の完了後、オート ゼロラインはロー(low)に戻る一方、選択ラインはハ イ (high) のままである。

【0028】第三フェーズはデータ書き込みフェーズで ある。データはベースライン電圧を超える電圧としてデ ータラインへ印加され、コンデンサを介して画素に書き 込まれる。次に選択ラインがローに戻り、データ電圧、 プラスLEDターンオン電圧、プラスN2の閾値電圧の 合計が、残りのフレームに関してノードBに保存され る。保存されたデータがリークによって失われないよう に、ノードBから+Vaaまでのコンデンサを使用できる ことに注目すべきである。

【0029】要するに、オートゼロフェーズの間、細電 流 (trickle current) を使用して、LEDのターンオ ン電圧とN2の閾値電圧が「測定」され、ノードBに保 存される。このオートゼロフェーズは、本質的には駆動 電流が極めて小さい電流駆動モードの作動である。オー トゼロフェーズの後の書き込みフェーズになって初め て、印加されたデータ電圧を使用してLEDに増分が与 えられる。従って、本発明は、電圧駆動または電流駆動 よりはむしろ、「ハイブリッド駆動」を有するというこ とが出来る。ハイブリッド駆動方法は、電圧駆動および 電流駆動における欠点がなく、両者の長所を組み合わせ るものである。LEDのターンオン電圧とTFTの閾値 電圧の変動は、電流駆動における場合と全く同様に補正 される。同時に、ディスプレイ上のすべてのラインは電 圧によって駆動されるので、高速で駆動することが出来 る。

【0030】注目べきことに、データライン360に印 加されるデータ電圧の増分は、LED304全体にわた って直接現れるのではなく、N2(320)とLEDの Vgs間に分割される。このことは単に、データ電圧から LED電圧への非線型のマッピングがあることを意味す る。このマッピングは、LED電圧からLED電流への 非線型のマッピングと組み合わされて、データ電圧から LED電圧への全体の伝達関数を発生するが、これは単 調で、上記のようにディスプレイの全寿命にわたって安 定している。

【0031】現在の画素構造300の利点は、閾値が補 正されない画素におけるトランジスタ(N3、N4およ びN5) がフレームあたり1列時間のみオンとなるため

シフトしないと予想されることである。更に、N2は、 LEDの現在パスにおける唯一のトランジスタである。 このパス上で直列接続されたトランジスタは、ディスプ レイ効率を劣化させるか、あるいは未補正のTFT閾値 シフトによる問題を発生する可能性があり、もしも一つ の列上の全部の画素によって共有されると、縦方向の著 しいクロストークをもたらす可能性がある。

【0032】選択パルスとオートゼロ(AZ)パルスは 行スキャナによって形成される。列データはAZパルス 同士間のタイムスロットにおいて (任意の) 一定ベース 10 ライン電圧に加えて印加される。選択信号の下降エッジ は、データライン上でデータが有効である間に発生す る。直接サンプル・タイプまたはチョップト・ランプ・ タイプのいずれかの各種の外付けまたは内蔵の列スキャ ナが、このタイミングによってデータを発生することが 出来る。

【0033】上記の画素構造によれば、有機LEDを使 用して大型の直視ディスプレイを造ることが出来る。も ちろん、現在の画素構造は、駆動電流を必要とするディ スプレイ要素を使用する任意のディスプレイ技術にも、 特にディスプレイ要素またはTFTのターンオン電圧が シフトするかまたは不均一である場合、適用可能であ

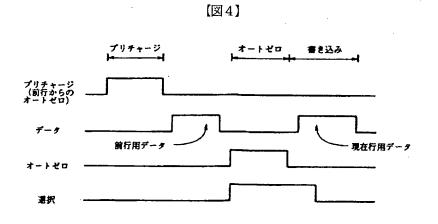

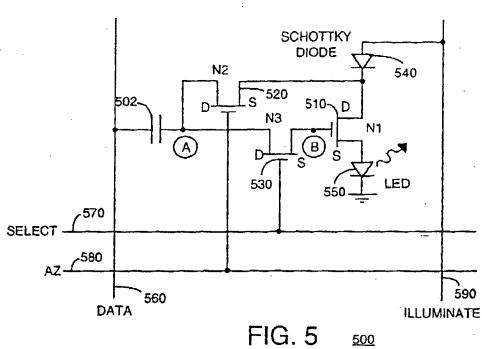

【0034】図5は、本発明によるアクティブマトリッ クスLED画素構造500の好ましい実施態様の略図で ある。この画素構造500は、図3の画素構造300に 類似であるが、ここでは2個のトランジスタの代わりに ショットキダイオード1個を使用している。

【0035】画素構造300が有する可能性のある欠点 の一つとして、1画素あたり5個のトランジスタを使用 30 していることが挙げられる。すなわち、各画素に多数の トランジスタを使用しているので、画素のフィルファク タ (fill factor) (アクティブプレートを通るボトム 側放出を想定して) およびその収率 (yield) にも影響 を及ぼす可能性がある。従って、画素構造300は、各 画素に1個のショットキダイオードのみを使用してトラ ンジスタ数を5個から3個に減らしつつ、且つ上記と同 じ機能を果たす。

【0036】図5において、画素500は3個のNMO SトランジスタN1 (510)、N2 (520)、N3 40 (530)、1個のコンデンサ502、1個のショット キダイオード540、およびLED (OLED) 550 (光要素) から成る。選択ライン570はトランジスタ 530のゲートに接続されている。データライン560 はコンデンサ502の一方の端子に接続されている。オ ートゼロライン580はトランジスタ520のゲートに 接続されている。点灯ライン(VDDラインに類似) 5 90はショットキダイオード540の一方の端子に接続 されている。

Aにおいて) トランジスタ520と530のドレインに 接続されている。トランジスタ530のソースは (ノー ドBにおいて) トランジスタ510のゲートに接続され ている。トランジスタ510のドレインはトランジスタ 520のソースと、ショットキダイオード540の一方 の端子に接続されている。

【0038】画素構造500も、下記のように、プリチ ャージフェーズ、オートゼロフェーズ、およびデータ書 き込みフェーズの3フェーズで作動する。すべての点灯 ラインはディスプレイの周囲で相互に結合されていて、 プリチャージフェーズが始まる前に、これら点灯ライン は、約+15Vのプラスの電圧VILLに保持される。以 下の説明においては、考慮中の行を「行i」と呼ぶ。各 ライン上の波形も図6に示す。

【0039】第一フェーズはプリチャージフェーズであ る。プリチャージは、オートゼロ(AZ)ラインがトラ ンジスタN2をオンにし、選択ラインがトランジスタN 3をオンにすると開始される。このフェーズは、データ ラインがリセットレベルにあるとき行なわれる。ノード AとBにおける電圧はトランジスタN1のドレインと同 じ電圧まで上昇するが、これはVILLより低いダイオー ド降下である。

【0040】第二フェーズはオートゼロフェーズであ る。次に、点灯ラインがアースに落ちる。このフェーズ 中、アレイ上のすべての画素は短時間暗くなる。ここ で、ショットキダイオード540がトランジスタN1の ドレインを、アースされた点灯ラインから絶縁して、N 1のオートゼロ化が始まる。ノードBがトランジスタN 1の閾値電圧プラスLED550のターンオン電圧にほ ぼ等しい電圧に達すると、AZラインを使用してトラン ジスタN2を「オフ」にし、点灯ラインはV!!!に戻 る。選択されなかった行のすべての画素が再び点灯す

【0041】第三フェーズはデータ書き込みフェーズで ある。次に、行iに関するデータがデータラインに印加 される。ノードAとBにおける電圧上昇が、データライ ンのリセット電圧レベルとデータ電圧レベル間の差を等 しくする。このようにして、トランジスタN1の閾値電 圧とLEDのターンオン電圧の変動が補正される。ノー ドBにおける電圧が落ち着いた後、行iに関する選択ラ インを使用してトランジスタN3をオフにし、データラ インがリセットされる。これで次のフレームまで適切な データ電圧が画素に保存される。

【0042】以上、先に述べた5トランジスタ画素の利 点を持ちつつも、トランジスタ数の少ない、OLEDデ ィスプレイ用3トランジスタ画素について説明した。 更 なる利点として、5トランジスタ画素には、オートゼロ 化とLED駆動とに別々のトランジスタを使用されるこ とである。画素300が適切に作動するには、これら2 【0037】コンデンサ502の一方の端子は(ノード 50 個のトランジスタの初期閾値が一致し、寿命の全期間に

わたって同じようにドリフトすることが必要である。最近の実験データが示唆するところによれば、(これらトランジスタのように)TFT同士のドレイン電圧が互いに異なると、両TFTは同様にはドリフトしない。従って、画素500は、適切なオートゼロ化が保証されるように、LEDを駆動する同じトランジスタ上でオートゼロ化を行なう。

【0043】図7は、本発明によるアクティブマトリックスLED画素構造700の代替実施態様の略図である。この画素構造700は、図3の画素構造300に類 10似するが、更に正確なオートゼロ電圧を発生する。

【0044】すなわち、図3において、オートゼロ化は、各プリチャージサイクルが図3に示すように大きなプラス電荷QPCを画素300のノードAに注入するという事実から生ずる。プリチャージフェーズ中、ノードA上のキャパシタンスのほとんどすべてはコンデンサCdataからであり、ノードAに注入される電荷は式(1)で表される。

[0045]

【数1】

$$Q_{pc} \cong C_{data} (V_{DD} - V_A) \tag{1}$$

【0046】ここでVaは、プリチャージフェーズが始まる前のノードAにおける電圧である。Vaは、画素300に予め与えられたデータ、N3(300)の関値電圧、およびLED304のターンオン電圧に左右される。Cdataが大きなキャパシタンス(約1pF)であるので、Qpcも10ピコクーロン(picocoulomb)程度と大きい。

【0047】画素300が安定したオートゼロレベルに 30 あるとき、Qpcはオートゼロフェーズ中、N1 (30 0)とLED304とを通って流れる。オートゼロ間隔 (インタバル) は短いので (約10μsec)、N1には その関値電圧より高いゲート対ソースオートゼロ電圧が 残る可能性があり、同様にLEDもそのターンオン電圧 を上回ってオートゼロ化する。このように、オートゼロ 化プロセスにおいては、ノードAとノードBで、真のゼロ電流オートゼロ電圧ではなく、その近似値を発生する 可能性がある。

【0048】注目すべきことは、N1とLEDを通る正 40 確なゼロ電流に対応する真のゼロ電流オートゼロ電圧を発生させる必要がないという点である。本発明において、微弱な電流(約10ナノアンペア)をN1 300とLED 304とを通って流すことの出来るオートゼロ電圧を得ることが望ましい。オートゼロ間隔(インタバル)は約10μsecであるので、Qpcは約0.1ピコクーロン程度のはずである。上記のように、Qpcは約10ピコクーロンである。

【0049】このように大きなQpcの効果として、画素の安定オートゼロ電圧が関値電圧とターンオン電圧の合 50

計をはるかに上回る可能性がある。この状態そのものは、もしも過剰なオートゼロ電圧がディスプレイ全体にわたって均一であれば、問題にはならない。すなわち、すべてのデータ電圧を相応にオフセットすることによって、この効果に対処することが出来る。

【0050】しかし、もしもQPCが大きいのみならず、前のデータ電圧とオートゼロ電圧そのものに左右される場合、問題を生ずる可能性がある。この状態がもしもディスプレイ内で発生すると、すべての画素のオートゼロ電圧が大幅に過剰になるのみならず、過剰電圧の大きさが画素ごとに異なる可能性がある。実際、そのような条件下では、画素300のオートゼロ化によって均一なディスプレイを作ることが出来ない。

【0051】この問題に対処するため、画素700はプ

リチャージQpcを極めて小さい値に下げることが出来る。また、オートゼロ化に実際に必要な電荷に応じてQpcを変化させることの出来る「可変プリチャージ」方法を開示する。要するに、現在のオートゼロ電圧が低すぎる場合、、オートゼロ電圧を所望の値にまで上げるため、Qpcはその最小値、約0.1ピコクーロンとなる。しかし、現在のオートゼロ電圧が高すぎると、Qpcは実質的にゼロになり、オートゼロ電圧が急速に下がることを可能にする。

【0052】図7を参照すると、画素700は、5個のNMOSトランジスタ、N1 (710)、N2 (720)、N3 (730)、N4 (740)、N5 (750)と、コンデンサ702と、LED (OLED) 704 (光要素)とから成る。選択ライン770はトランジスタ710のゲートに接続されている。データライン760はコンデンサ702の一方の端子に接続されている。オートゼロライン780はトランジスタ740のゲートに接続されている。VDDライン790はトランジスタ720と750のドレインに接続されている。画素アレイ内の前の行からのオートゼロライン782はトランジスタ750のゲートに接続されている。

【0053】本発明において、前の行からのオートゼロラインを第二選択ラインとすることが出来ることが特徴である。すなわち、現在の画素のタイミングを、第二選択ラインを必要とせずに前の行からのオートゼロライン782を利用できるようなタイミングにして、現在の画素の複雑さとコストを低減することが出来る。

【0054】コンデンサ702の一方の端子は(ノードAにおいて)トランジスタ710のドレインに接続されている。トランジスタ710のソースは(ノードBにおいて)トランジスタ720、730のゲートに接続され、トランジスタ740のドレインは(ノードCにおいて)トランジスタ750のソースとトランジスタ730のドレインに接続されている。最後に、トランジスタ730、720のソースはLED704の一方の端子に接続され

ている。

【0055】更に具体的に、画素700は、トランジスタN3(730)のドレインであるノードCにプリチャージ電圧が印加されること以外は、画素300に類似する。更に、図8に示すようないくつかのタイミング変更もある。以下に、画素700の作動を3フェーズの段階に分けて説明する。

【0056】第一フェーズは前のラインタイム中、すなわちデータが前の行の画素に印加される前に行なわれるプリチャージフェーズである。選択ライン上のプラスの10パルスがN1を「オン」にし、これによってノードAとBが互いにショートされ、画素700の状態が、直前のオートゼロフェーズの後の状態に戻る。すなわち、画素は、画素の適切なオートゼロ電圧の最近の推測値である、データに依存しない電圧に戻る。N1が「オン」である間、前の行ラインからのオートゼロライン782上の正のパルスがトランジスタN5を「オン」にし、これによってノードCをVdはにプリチャージする。次に、トランジスタN1とN5が「オフ」とされる。

【0057】トランジスタN1とN5のオン、オフの相 20 対的タイミングは、あまり重要ではないが、トランジスタN1は、トランジスタN5がオフになる前にオンとしなければならない。そうしないと、トランジスタN3が旧データ電圧に応じて依然としてオンのままとなり、ノードCへ注入された電荷がトランジスタN3を経てリークしてしまう可能性がある。

【0058】 プリチャージフェーズの後、電荷Qpcはノ ードCにおいて、トランジスタN3、N4、N5のゲー ト対ソース/ドレインのキャパシタンス上に保存され る。これらキャパシタンスの合計は極めて小さく(約1 30 Of F) 、また、プリチャージ間隔がノードCを約10 V上昇させるので、QPCは当初、約0.1ピコクーロン である。しかしこの電荷は、前のオートゼロ電圧の真の オートゼロ電圧に対する近似精度によって変化する割合 で、オートゼロフェーズの前にノードCからリークす る。従って、オートゼロ化のためにはどれ程の電荷量が 必要かということ次第で、Qpc≦0.1ピコクーロンの 関係はより精確に示されることになる。これは可変プリ チャージ特徴である。直前のオートゼロ電圧が低すぎる 場合、N3はプリチャージフェーズ後、非導通となり、 QPCはその最大値に留まるはずであり、オートゼロフェ ーズ中、オートゼロ電圧をその要求レベルに向かって上 昇させる。直前のオートゼロ電圧が高すぎる場合、N3 は導通し、QPCはオートゼロフェーズが始まるまでには リークし、オートゼロ電圧の急低下が可能になる。

【0059】トランジスタN1とN5の相対的タイミングは重要ではないが、好ましいタイミングを図8に示す。プリチャージに要する時間を最短にするため、2個のトランジスタN1とN5は同時にオンとされる。N1はN5より前にオフとされるが、これにより、ノードC50

からのQrcの(意図的な)リークは、N1をオフにすることによって容量的に押し下げられたノードB電圧に対応する。これにより、ノードCからのQrcのリークは、画素にゼロデータが印加されたときに等しいノードB電圧に確実に対応する。

【0060】要するに、画素700は、画素300に比してより効果的なオートゼロ化を可能にする画素のプリチャージ手段を提供する。具体的には、画素700のオートゼロ化は、より正確、迅速、かつデータに対して独立性である。コンピュータシミュレーションによる確認では、画素700は、オートゼロ化が良好であり、10、000時間の作動寿命の全期間にわたってほぼ一定のOLED電流対データ電圧特性を維持することが出来る。

【0061】図9は、本発明の他の実施態様であるアクティブマトリックスLED画素構造900の略図である。画素構造900は、図7の画素構造700に類似しているが、追加のVprechargeライン992を備え、LED供給電圧Vddを上げずにオートゼロ電圧範囲を拡張することが出来る点が異なる。画素のこの追加修正は、画素の寿命と効率を改善する。

【0062】以上説明した画素(200、300、700)は、Vddがプリチャージ電圧であるので、オートゼロ電圧がVddを超えることが出来ないという制限がある。しかし、トランジスタN2とN3の閾値電圧がトランジスタの寿命期間にわたってドリフトし、TFTドリフト電圧とOLEDターンオン電圧のドリフトを補正するため、オートゼロ電圧をVddより高くする必要が生じる点に到達する。オートゼロ電圧は、より高い電圧に到達することは出来ないので、ディスプレイの均一性は急速に劣化し、ディスプレイの有用寿命の終りを告げる。Vddを高くすれば、より高いオートゼロ電圧を達成できるが、VddはOLED駆動電源でもあるので、パワー効率が犠牲になる。

【0063】更に、パワー効率の改善のため、Vadを下げてトランジスタN2をライン形領域で作動させると、オートゼロ電圧の範囲は更に制限される。(もちろん、そのようにすると飽和状態で作動させた場合よりN2を大きくする必要がある。)この場合、短時間の作動の後、オートゼロ電圧はVadより高いレベルに到達する必要があるので、駆動寿命は極めて短くなる。

【0064】図9を参照すると、画素700に、オートゼロ電圧に対する制限をなくし、それによってVddを十分に上回ることを可能にするオプションの変更が組込まれている。画素900は、列ライン992が追加され、それがトランジスタ950のドレインに接続されている以外は、画素700と同じである。

【0065】列ライン992は、DC電圧Vprecharge をすべての画素に運ぶため、アレイに追加されている。 これらすべての列ラインは、ディスプレイの端で相互接 続されている。VprechargeをVddより高いレベルに上げることによって、画素900は、Vprechargeより高い電圧にプリチャージを行ない、オートゼロ化することが出来る。の高い値は、ディスプレイ効率にほとんど影響を及ぼさない。

【0066】各Vprechargeライン992は、画素の隣接する列との共有が可能であることに注目すべきである。このVprechargeラインはまた、行ラインとして走らせ、隣接する行との共有が可能である。

【0067】要するに、オートゼロ電圧の範囲をVddを 10 超えて拡張するため、追加の電圧ラインを備えたOLE D画素を開示する。これによってOLED駆動トランジスタは、パワー効率上必要な低い電圧で、場合によってはライン形領域においてすら、オートゼロ電圧を制限することなく、作動することが出来る。従って、長い作動寿命と高効率が達成できる。この変更を画素700について説明したが、最終的には、このオプション変更は、上記画素200、300を含み、それらに限らない他のオートゼロ画素構造にも実施可能である。

【0068】上記各画素構造は、OLEDディスプレイ 20 用として、画素におけるトランジスタ閾値電圧変動とOLEDターンオン電圧変動が補正されるように設計されているが、これら画素構造は、画素の外部で発生する不均一性に対処するようには設計されていない。この画素は、ディスプレイプレートの外部からでも、ディスプレイに一体化した状態でも、従来の列駆動回路に使用可能であることが指摘された。

【0069】残念ながら、一体型データドライバは、外 付けドライバほど精度がよくないのが普通である。市販 の外付けドライバでは±12mVの精度を達成できる が、一体型ドライバでは±50mVの精度を達成できな いことが判明している。一体型ドライバに特有なタイプ の誤差は、オフセット誤差、すなわち、すべてのデータ 電圧に加えられる、データ非依存性のDCレベルであ る。このオフセット誤差は不均一、すなわちDCレベル の値はデータドライバごとに変動する。液晶ディスプレ イはオフセット誤差を許容する傾向がある。その理由 は、フレームが順次反対極性で駆動され、あるフレーム でオフセット誤差が液晶をわずかに暗くし、次のフレー ムで明るくするが、平均的にはほぼ正確で、交互の誤差 40 は目で認識できないからである。しかし、OLED画素 は単一極性データによって駆動される。従って、オフセ ット誤差の二極消去は発生せず、一体型スキャナを使用 すると深刻な不均一性問題が発生する可能性がある。

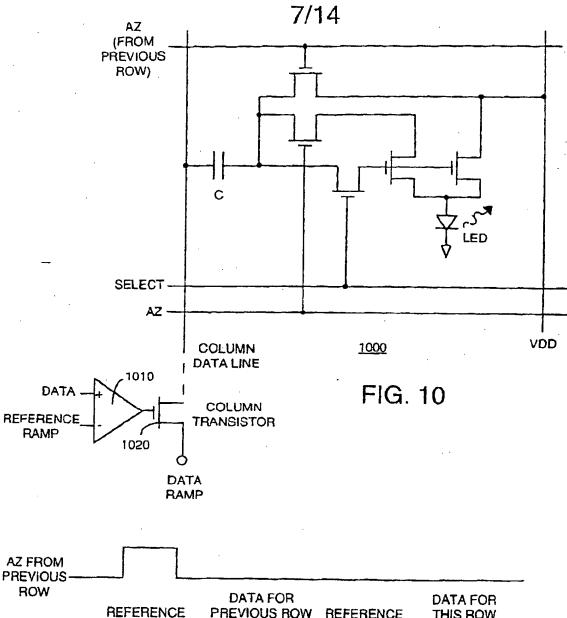

【0070】図10は、列トランジスタ1020を介してデータドライバ1010に接続された本発明のアクティブマトリックスLED画素構造300の略図である。本発明は、OLEDディスプレイ用の一体型データスキャナにおけるオフセット誤差の消去方法を説明する。すなわち、この方法は、画素がデータラインに容量的に接50

続され、例えば上記の画素200、300、500および700のようなオートゼロフェーズを有する任意の画素とともに作動するように設計されている。

【0071】図10を参照すると、上記の画素300は、OLED要素の輝度を確定するため画素にアナログレベルを供給するデータラインに接続されている。図10において、データラインは、データライン上に電圧を設定するためのチョップト・ランプ技法(chopped ramp technique)を使用するデータドライバによって駆動される。このアプローチ(技法)には、データライン上にオフセット誤差を発生させる種々の誤差源が存在する。例えば、電圧比較器が切り替わる時間は、比較器の最大スルーレート(slew rate)次第で変動する可能性がある。また、最大スルーレートは大幅に変動することが、実験によって観察されている。オフセット誤差は、画素に保存されている電圧に影響を及ぼす。オフセット誤差はまた、不均一であるので、ディスプレイ全体にわたって輝度の変動をもたらす。

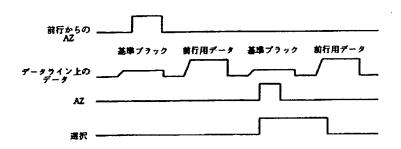

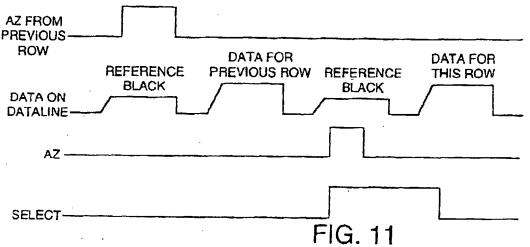

【0072】本発明においては、画素がそれ自体の内部 関値誤差を消去するためのオートゼロ化の期間を、デー タスキャナのオフセット誤差のキャリブレーションにも 使用する。種々のラインの波形を図11に示す。

【0073】すなわち、これは実際のデータ電圧を印加するのと同じ列ドライバを使用してデータライン上に基準ブラックレベルを設定することによって達成される。画素のオートゼロフェーズ中に印加されるこの基準ブラックレベルは、実際のデータ電圧が設定されるのと全く同じやり方でデータライン上に設定される。すなわち、データランプ(data ramp)は電圧比較器によって定められる時間においてチョップされる。従って、画素のコンデンサCを横切る電圧は画素のターンオン電圧と、ブラックレベルにオフセット誤差電圧をプラスした組合せによって定まる。基準ブラックレベルは、オートゼロフェーズの全期間、維持される。実際のデータが画素に印加されると、データスキャナオフセット誤差は画素のコンデンサ上に保存された電圧によって消去される。

【0074】この技法は、チョップト・ランプを使用する一体型スキャナのみならず、列上へ直接サンプリングを使用するスキャナにも適用可能である。直接サンプリングの場合、誤差は、(大きな)列トランジスタがオフにされるとき、ゲート信号のデータラインへの不均一容量フィードスルーによって発生する。このトランジスタの閾値電圧変動は、チョップト・ランプ・データ・スキャナによって生じる不均一オフセット誤差と全く同様に、不均一オフセット誤差を生じる。

【0075】従って、これは同様に補正できる。ブラック基準電圧は、画素のオートゼロフェーズ中、列に書き込まれる。一行のすべての画素が同時にオートゼロ化するので、このブラックレベルは、ラインタイム開始時にすべてのデータ列に同時に書き込まれる。ブラックレベ

ルはオートゼロフェーズの全期間中、維持される。チョップト・ランプ・スキャナの場合のように、実際のデータが画素に印加されると、オフセット誤差は画素キャパシタに保存されている電圧によって消去される。しかし、オフセット誤差の補正に必要な時間オーバーヘッドは、チョップト・ランプ技法を使用するよりも、直接サンプリング技法を使用する方が少ないように思われる。【0076】データドライバ誤差を補正するための本発明の方法は、別の方法よりも輝度の均一性のはるかに良好な有機LEDディスプレイの作成を可能にするはずである。ここに説明した方法と、上記いずれかのオートゼロ化画素を使用して、ディスプレイの全寿命にわたって均一性に目立った劣化のない、8ビットの輝度均一性が達成可能である。

【0077】上記開示では、ディスプレイの輝度の不均一性に対処するため使用することの出来る複数の画素構造を記述したが、代替のアプローチ(技法)として、外付け手段によって不均一性を補正することが出来る。より具体的には、下記の開示は、ディスプレイの輝度の不均一性に対処するための方法と外付けキャリブレーショ 20ン回路を説明する。要するに、すべての画素について不均一性を測定し保存し、測定した不均一性を使用して、データ(例えばデータ電圧)のキャリブレーションを行なうことが出来る。

【0078】このように、以下の説明においては、図2の従来の画素構造を使用するが、本発明の外付けキャリブレーション回路と方法は、上記の画素300、500、700を含み、これらに限らない他の画素構造にも使用することが出来る。しかし、本発明の外付けキャリブレーション回路と方法によって不均一性に対処すれば、より簡単な画素構造をディスプレイに採用でき、それによってディスプレイの収率とフィルファクタ(fill-factor)を増加させることが出来る。

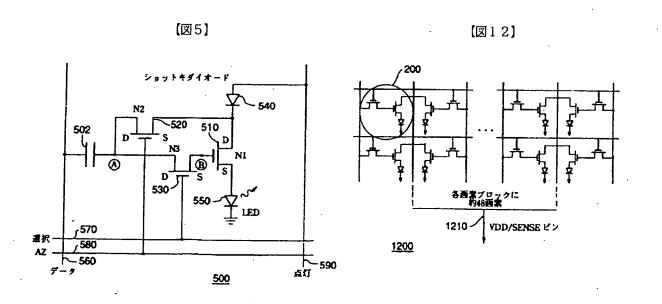

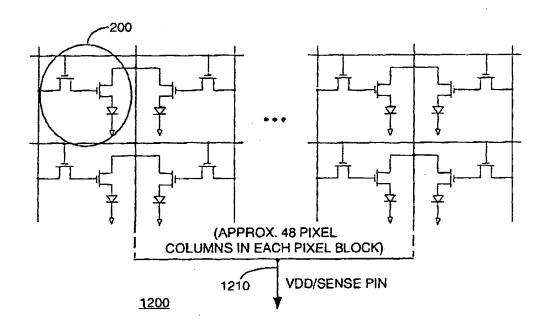

【0079】図12は、画素200のアレイ(集合)を 相互接続して画素ブロック1200とした状態の略図で ある。図2を参照すると、動作の際、データは、アクテ ィブマトリックスディスプレイで普通に行なわれる方法 で、画素アレイに書き込まれる。すなわち、選択ライン を高く駆動することによって画素の一行が選ばれ、それ によってアクセストランジスタN1がオンとなる。各デ 40 ータラインにデータ電圧を印加することによって、この 行の各画素にデータが書き込まれる。ノードAにおける 電圧が安定した後、選択ラインを低く駆動することによ って、この行が選択から解除される。このデータ電圧 は、次のフレームでこの行が選択されるまで、ノードA に保存される。N1がオフにされている間に、ノードA から多少の電荷リークの可能性があるので、不適当なレ ベルの電圧降下を防ぐため、ノードAに蓄電コンデンサ が必要になるかも知れない。図中の破線は、電圧降下に 対処するための、コンデンサの接続方法を示す。しか

し、そのような追加のコンデンサを不要にするほど十分 なキャパシタンスがN2のゲートに関連して存在するか もしれない。

【0080】注目すべきことに、OLEDの輝度Lは、その電流Iにほぼ比例し、比例定数はディスプレイ全面にわたってかなり安定している。従って、良好に確定されたOLED電流を発生させれば、ディスプレイは視覚的に均一になる。

【0081】しかし、プログラムによって画素へ供給されるのは、OLED電流ではなくN2上のゲート電圧である。TFT関値電圧と相互コンダクタンス(transconductance)は、OLEDの電気的パラメータが呈するように、ディスプレイ全体にわたる多少の初期不均一性を呈する可能性がある。更に、TFT関値電圧は、OLEDターンオン電圧と同様に、バイアス温度ストレス条件下で増加することが周知である。従って、これらのパラメータは、当初不均一であり、各画素の個々のバイアス履歴に依存する態様で、画素の全寿命にわたって変化するものと期待される。これらパラメータを補正せずにN2のゲート電圧のプログラムを作成すると、ディスプレイは当初から不均一で、ディスプレイの全寿命にわたって不均一性が次第に増大する。

【0082】本発明は、TFTとOLEDの電気的パラメータが補正され、それによって良好に確定されたOLED電流が画素アレイ内に生じるような方法である。N2に印加されるデータ電圧を補正するための方法を以下に説明する。

【0083】図2と図12は、データラインに並列に配置されたVDD供給ラインを有する画素アレイを示す。(好ましい実施態様において、VDDラインは選択ラインに並列に配線することが出来る。)このようにして、画素が2個またはそれ以上の隣接する列で各VDDラインを共有して、VDDラインの本数を減らすことが出来る。図12は、VDDラインがディスプレイの周囲で結束されてブロック化された状態を示す。各画素ブロック1200に含まれるVDDラインの数は、1本と少なくても、ディスプレイ上のVDDラインの全数のように多くてもよい。しかし、好ましい実施態様において、各画素ブロック1200は、約24本のVDDライン、すなわち約48の画素列を含む。

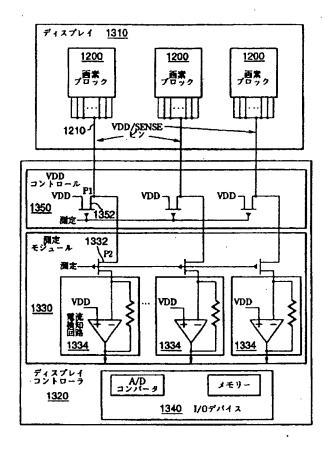

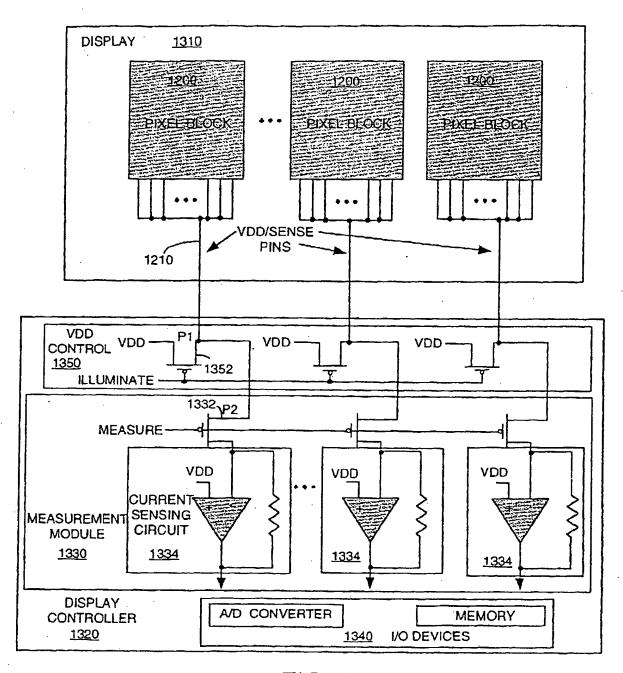

【0084】図13は、ディスプレイ1310とディスプレイコントローラ1320との相互接続の略図である。ディスプレイ1310は複数の画素ブロック1200から成る。ディスプレイコントローラ1320は、VDDコントロールモジュール1350、測定モジュール1330、および種々のI/Oデバイス、例えばA/Dコンバータや、画素パラメータを保存するためのメモリーから成る。

【0085】各画素ブロックは、図12、13に示すよ 50 うに、ディスプレイの端において検知ピン(VDD/S ENSE) 1210に接続されている。通常のディスプレイ作動中、検知ピン1210は、例えば10ないし15ボルトの外部Vdd電源に切り替えられ、これによってOLEDエレメントを点灯するための電流をディスプレイに供給する。更に具体的には、各VDD/SENSEピン1210は、ディスプレイコントローラ1320において、一対のpチャンネルトランジスタP1(1352)とP2(1332)および電流検知回路1334に接続されている。通常の作動中、ディスプレイコントローラからのILLUMINATE信号がP1を作動させ10てVDD/SENSEピンをVdd電源に接続する。典型的な実施態様において、P1を通る電流は約1mA/列と予想される。

【0086】TFTとOLEDのパラメータを補正するため、特別測定サイクル中、各画素のパラメータに関する情報を収集するため、MEASURE信号を介して外付け電流検知回路1334を作動させる。収集された情報は、通常のディスプレイ作動中、必要なOLED電流を実現するのに適したデータ電圧の計算および調整に使用される。

【0087】更に具体的には、特定の画素の測定サイクル中、画素ブロック内の他のすべての画素は、それらに低いデータ電圧(例えばゼロ以下)を印加することによって、オフにされ、それによって、「オフ」画素からの電流の引き出しを確実に無視できるようにする。次に、対象とする画素によって引き出された電流が、1個以上の印加データ電圧に応じて測定される。各測定サイクル中、データパターン(すなわち、あるブロック中で、1個の画素のみがオンで、その他すべての画素がオフ)が、通常の方法で画素に印加され、データドライバ回路 30によってデータがDATAラインに印加され、行が一つずつ選択される。このようにして、ディスプレイが複数の画素ブロックに区画されるので、各画素ブロック内の少なくとも1個の画素をオンにすることによって、複数の画素を測定することが出来る。

【0088】各画素プロック内の対象画素によって引き出された電流は、ILLUMINATEラインとMEASUREラインを、VDD/SENSEピン1210をVDD電源から切り離すとともに検知ピンをP2経由で電流検知回路1334のインプットに接続するレベルに40駆動することによって外部からP2において測定される。画素電流は1ないし10μAと予想される。電流検知回路1334は図13に相互インピーダンス増幅器として示してあるが、電流検知回路を他の形態で実施することも出来る。本発明においては、増幅器は入力端における電流に比例した電圧を出力端に発生する。この測定された情報は、I/Oデバイス1340によって収集され、そこでこの情報はディジタル形式に変換され、データ電圧のキャリプレーション用に保存される。電流検知回路1334内の抵抗器は約1メガオームである。50

【0089】複数の電流検知回路1334が画素ブロックと一対一の対応で示してあるが、マルチプレックサ(multi-plexer、不図示)を使用すれば、電流検知回路の数を減らすことが出来る。すなわち、複数のVDD/SENSEピンを単一の電流検知回路1334に多重化することが出来る。極端な場合、単一の電流検知回路を全ディスプレイ用に使用することが出来る。VDD/SENSEピンをこのように検知回路に多重化すると、外付け回路の複雑さは低減できるが、ディスプレイ測定時間は長くなる。

【0090】画素測定サイクルを行なうためには、通常のディスプレイ作動を中断しなければならないので、画素測定は、見る人を出来るだけ邪魔しないようにタイミングを図らねばならない。画素パラメータは徐々に変化するので、特定の画素を頻繁に測定する必要はなく、測定サイクルは長期間にわたって分散することが出来る。【0091】すべての画素を同時に測定する必要はないが、可変測定ラグ(遅延)に基づく不均一性を避けるた

が、可変測定ラグ(遅延)に基づく不均一性を避けるた めには、同時測定が有利である。これは、ディスプレイ モジュールが「オン」または「オフ」されるとき、すべ ての画素を迅速に測定することによって達成可能であ る。ディスプレイモジュールが「オフ」のとき画素を測 定すれば、通常の作動の邪魔にはならないが、長い「オ フ」期間後、保存された画素パラメータはもはや均一性 を保証しないかも知れないという欠点がある。しかし、 中断しない電源が利用可能であれば(例えばスクリーン セイバーモードにおいて)、ディスプレイが (ユーザー の観点から)「オフ」である間に測定サイクルを周期的 に行なうことが出来る。もちろん、ディスプレイモジュ ールが「オン」のときすべての画素の迅速測定を含まな い任意のオプションでは、パワーが「オフ」のとき測定 情報を保存するための不揮発性メモリーが利用可能であ ることが必要である。

【0092】もしも画素測定情報が利用可能であれば、ディスプレイの不均一性の種々の原因を補正するため、データ電圧の補正またはキャリブレーションをディスプレイに適用することが出来る。例えば、トランジスタの関値電圧変動とOLEDターンオン電圧変動に対処するため、データ電圧の補正を行なうことが出来る。従って、上記およびその他のディスプレイ不均一性を補正することの出来る複数の方法を以下に説明する。これらの方法を使用すれば、ディスプレイに数個の、そのうちのいくつかは大きな不均一性の原因があっても、均一な高画質ディスプレイを提供することが出来る。

【0093】この補正方法を説明するため、ディスプレイには図2の画素構造を使用するものと仮定する。しかし、この補正方法は、他の任意の画素構造を使用したディスプレイにも適用できる。

【0094】図2を参照すると、ノードAに保存された 50 電圧はN2のゲート電圧であり、従ってN2とLEDと

\*

10

を通る電流を確定する。N2上の電圧を変化させること によって、LED電流を変化させることが出来る。N2 上のゲート電圧とLEDを通る電流との関係を考慮す る。ゲート電圧Vgは、以下の式(2)の様に、N2の ゲート対ソース電圧Vgsと、LEDを横切る電圧V diodeの二つに分割することが出来る。

[0095]

【数2】

$$V_g = V_{gs} + V_{diode}$$

(2)

【0096】飽和状態のMOSトランジスタのドレイン 電流は以下の式(3)で表される。

[0097]

【数3】

$$I = \frac{2}{k} (V_{gs} - V_t)^2$$

(3)

【0098】 ここで、kはデバイスの相互コンダクタン スパラメータ、Vtは閾値電圧である(ライン形領域に おける作動は下記参照)。従って、以下の式(4)が得20 られる。

[0099]

【数4】

$$V_g = V_t + \sqrt{\frac{2I}{k}} + \sqrt{\frac{I}{A}}$$

(7)

【O106】OLEDのI-V特性を表すため、他の関 数形式を使用することも出来るが、上記の式によれば、 ゲート電流とダイオード電流との間の異なる関数関係を 30 もたらすことに注目すべきである。しかし、本発明は、 上記のOLEDのI-V特性の詳細な関数形に限定され ず、従って、任意のダイオード的特性に関して作動する ように適応させることが出来る。

【0107】OLEDの輝度しは、その電流Iにほぼ比 例し、比例定数は、ディスプレイ全面にわたって安定か つ均一である。良好に確定されたOLED電流を発生さ せることが出来れば、ディスプレイは視覚的に均一とな る。しかし、以上説明したように、画素は電流Iではな く、電圧Vgを使用してプログラムされている。問題 は、OLEDのパラメータAとmの他に、TFTのパラ メータVtとkがディスプレイ全面にわたって、ある程 度の初期不均一性を呈するという点である。更に、Vi がバイアス温度ストレス条件下で増加することは周知で ある。OLEDパラメータAは、OLEDのターンオン 電圧に直接関連し、バイアスストレス下で減少すること が知られている。OLEDパラメータmは、オーガニッ ク・バンド・ギャップ内のトラップの分布に関連があ り、OLEDの全寿命にわたって変化する。従って、こ れらのパラメータは初期に不均一であり、各画素の個々 50

$$V_{gs} = \sqrt{\frac{2I}{k}} + V_{t} \tag{4}$$

【0100】OLEDを通る前向き電流は以下の式

(5) で表される。

[0101]

【数5】

$$I = AV_{\text{diode}}^{m} \tag{5}$$

【0102】ここで、Aとmは定数である (Burrows 他 の J. Appl. Phys. 79(1996)参照)。従って、以下の式 (6) が得られる。

[0103]

【数6】

$$V_{diode} = \sqrt[m]{\frac{I}{A}}$$

(6)

【0104】従って、ゲート電流とダイオード電流との 全体的関係は、以下の式(7)で表される。

[0105]

【数7】

$$+ \sqrt[m]{\frac{I}{A}}$$

(7)

のバイアス履歴に依存してディスプレイの全寿命にわた って変化するものと予想される。これらのパラメータの 変動を補正せずにゲート電圧をプログラムすると、ディ スプレイは初期に不均一で、その全寿命にわたって不均 一性が増大する。

【0108】実際に、不均一性の原因は他にもある。ゲ - ート電圧Vgは、意図したデータ電圧Vdataに必ずしも 等しくない。むしろ、データドライバにおけるゲイン誤 差とオフセット誤差、およびN1の選択解除から発生す る(データ依存性の)フィードスルーが、これら二つの 電圧に差異を生じさせる。これらの誤差原因も、不均一 であり、かつ、ディスプレイの全寿命にわたって変動す 40. る。上記およびその他のゲイン誤差とオフセット誤差 を、以下の式(8)で表す。

[0109]

【数8】

$$V_g = BV_{data} + V_0 \tag{8}$$

【0110】ここで、BとVoはそれぞれゲイン係数と オフセット電圧であり、ともに不均一であり得る。式

- (7)と(8)を組み合わせて整理すると以下の式

- (9) が得られる。

- [0111]

【数9】

$$V_{data} = V_{off} + C\sqrt{I} + D\sqrt{T}$$

(9)

【0112】ここで、Vorr、C、Dは前出のパラメータの組合せである。

【0113】本発明は、Voff、C、D、およびmの変動を補正するため、意図する(入力)データ電圧を補正する種々の補正方法を提供し、それによって画素アレイ内における良好に確定されたOLED電流の発生を可能にする。パラメータVoff、C、D、およびmの変動を補正するため、上記の外付け電流検知回路が、各画素に関する情報、すなわち単一の画素によって引き出された電流を外部から測定することが出来る。パラメータVoff、C、D、およびmに関して測定された情報を使用して、本発明は、通常のディスプレイ作動中、必要なOLED電流を確定するため、式(9)に従って適切なデータ電圧Vdataを計算する。

【0114】また、電流の測定値から4個のパラメータ Voff、C、D、およびmを正確に計算することは、コ ンピュータでは高価になり、複雑な繰り返し計算が必要 20 になる。しかし、効果的な補正を維持しつつ計算の複雑 さを低減する良好な近似を使用することが出来る。

【0115】好ましい実施態様において、上記のように 4個ではなく、わずか2個のパラメータを使用して画素 の不均一特性を表すことが出来る。式 (9) の画素の電\*

$$V_{data} = V_{offset} + C - \sqrt{I}$$

(10)

【0118】ここで、Voffset = Voff + D<sup>™</sup>√ I はD<sup>™</sup>√ I を含み、VoffsetとCは画素ごとに変動する。

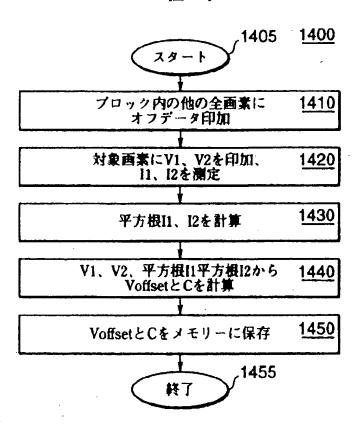

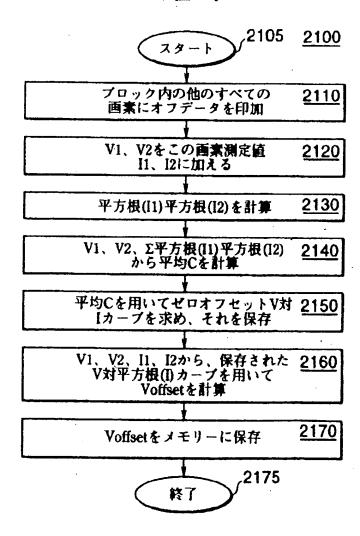

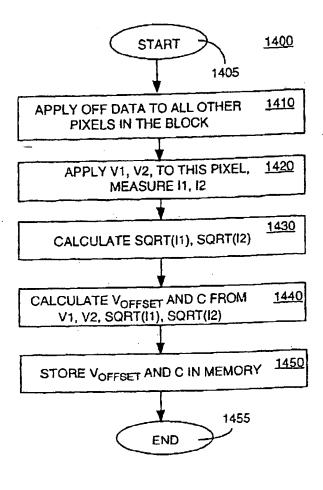

【0119】図14は、全画素のパラメータの測定によってディスプレイを初期化する方法1400のフローチャートである。方法1400は、ステップ1405から始まり、ステップ1410に進み、そこで、画素ブロック内の対象とする画素以外のすべての画素に、「オフ」データ電圧を印加する。

【0120】ステップ1420において、対象とする特定の画素のVoffsetとCを求めるため、方法1400は二つのデータ電圧(V1とV2)を印加し、各データ電圧について電流を測定する。

【0121】ステップ1430において、電流I1とI2の平方根が計算される。好ましい実施態様において、この計算のために平方根表が使用される。

【0122】ステップ1440において、VoffsetとCとが求められる。すなわち、二つの変数を求めるのに二つの式を使用することが出来る。次に、特定の対象画素の求められたVoffsetとCを記憶装置、例えばメモリーに保存する。全部の画素の測定が終ると、メモリーはアレイ内の各画素について二つのパラメータVoffsetとCとを保存している。これらの値は、後に式(10)を使 50

\*流電圧特性を参照すると、通常の点灯レベルにおいて、N2のVgsに関するC√I項と、Vdiodoに関するD<sup>m</sup>√I項とは、ほぼ同じ大きさである。しかし、それらの画素電流への依存性は大きく異なる。mの値は約10であるので、普通の点灯レベルにおいては、D<sup>m</sup>√IはC√Iに比してはるかに弱いIの関数である。例えば、Iを1010倍に増加させると、C√Iは10倍になるが、D<sup>m</sup>√Iは(mを10と仮定すると)1.58倍にしかならない。すなわち、普通の点灯電流レベルにおいては、OLEDのI-V曲線はTFTのI-Vgs曲線よりはるかに急勾配となる。

【0116】従って、普通の電流レベルにおいて、D<sup>n →</sup> √ I は電流に対して独立であり、その画素ごとの変動は単に一つのオフセット誤差として処理可能であるという近似が行なわれる。この近似は多少の誤差を持ち込むが、ディスプレイ全体の外観は大幅には劣化しない。従って、かなりの精度で、すべてのディスプレイの不均一性を、オフセットとゲインの変動として処理することが出来る。従って、(9)式は以下の式(10)の様に近似することが出来る。

(数10)

[0117]

用してVdataのキャリブレーションまたは調整に使用することが出来る。方法1400は次にステップ1455 30 において終了する。

【0123】測定される画素を通る電流は、D™√Iが 二つの測定点においてほぼ等しくなるように、十分に高 くなければならないことに注目すべきである。この条件 は、一方の測定を、システムが発生可能な最高データ電 圧において行ない、次に他方の測定をわずかに低いデー タ電圧において行なうことによって満足させ得ることが 望ましい。

【0124】ディスプレイの初期化が行なわれると、ディスプレイモジュールに供給された生の入力ビデオデー40 夕を修正することが出来る。入力ビデオデータは、例えば(1)画素電圧、(2)ガンマ補正された画素輝度、または(3)画素電流といった種々のフォーマットで存在することが出来ることに注目すべきである。従って、入力ビデオデータのキャリブレーションまたは補正を行なうための、保存されたパラメータVoffsetとCの使用は、各特定のフォーマットに依存する。

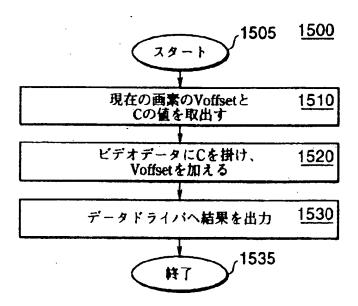

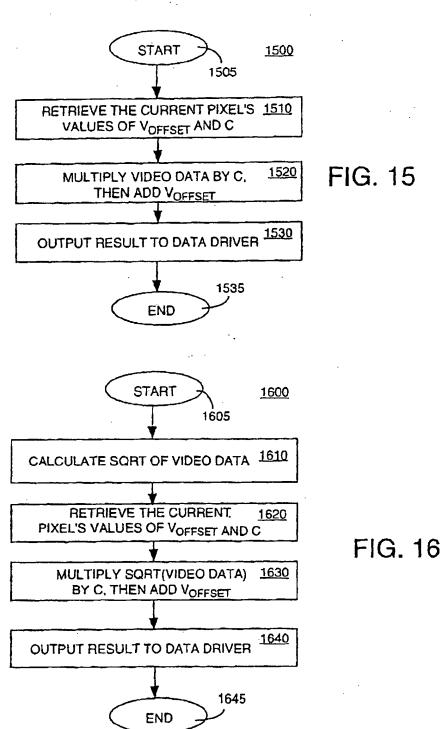

【0125】図15は、画素電圧を表す入力ビデオデータの修正方法1500のフローチャートである。方法1500は、ステップ1505から始まり、ステップ1510へ進み、そこで対象画素に関して保存されたパラメ

40

ータ、例えばVoffsatとCが取出される。

【0126】ステップ1520において、方法1500 は、入力ビデオデータのキャリブレーションを行なうた め、取出したパラメータを印加する。より具体的には、 入力ビデオデータにはバイアスがかかっていない、すな わち、ゼロボルトはゼロ輝度を表し、ゼロより大きいデ ータはゼロより大きい輝度レベルを表すものと期待され る。従って、電圧はCo√Iに等しいと見なすことが出 来る。ここで、Iは必要電流、Coは定数、例えば典型 的な値は103V/√Aである。入力ビデオデータがデ 10 ィスプレイモジュールに入る際の画素変動を補正するた め、各画素についてVoffset = Voff + C√I を、保存されたVoffsetとCに基づいて計算する。この 計算は、ビデオデータにC/Coを掛けることと、その 結果にVoffsetを加えることとから成る。Coによる除 法は、ビデオデータVdataが既に一定の係数1/Coに よって縮小されていれば不要である。Cによる乗法は、 ディジタルロジックで直接、またはルックアップテーブ ルを使用して行なうことが出来る。例えば、後者の場 合、Cの各値は、ビデオデータの値がインデックスであ 20 るとともにテーブルエントリーが乗法の結果であるテー ブルを指定する。(あるいは、ルックアップテーブル内 の入力ビデオデータとCの役割を逆にすることも出来 る。) 乗法が行なわれた後、ディジタルロジックにより Voffsetの急速加算が行なわれる。

【0127】ステップ1530において、得られた電圧 Vdata、すなわち修正または調整された入力データは、 画素アレイのデータドライバに送られる。方法1500 は次にステップ1535で終了する。

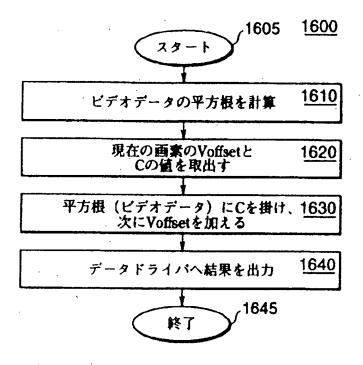

【0128】ガンマ補正された輝度データの場合、入力 30 ビデオデータは、L<sup>0.45</sup>に比例する。ここで、Lは輝度である。これは、CRT輝度-電圧特性に関して予め補正されたビデオデータでは典型的である。L<sup>0.45</sup>=√Lであり、また、OLED輝度はその電流に比例するので、データは√Iに比例するものとして処理することが出来る。従って、計算は先に説明したゼロオフセット電圧に関する方法と同様な方法で行なうことが出来る。

【0129】図16は、画素電流、すなわち輝度を表す入力ビデオデータの補正方法1600のフローチャートである。方法1600は、ステップ1605から始まり、ステップ1610に進み、そこで測定された電流の平方根の値が求められる。すなわち、方法1600は、Iを表すビデオデータが√Iを発生するように処理されねばならないこと以外は、上記の方法1500と同じである。上記のように、この演算は、図14に示すように、画素電流測定値から画素パラメータVoffsetとCを求めるのに必要な平方根の値を与える表を使用してビデオデータから√Iを発生させる。

【0130】次にデータ補正ステップ1610ないし1 50

645は、ステップ1630において入力データにCを掛け、次にVorrsetを加えて補正されたデータ電圧を求めること以外は、上記の方法1500と同一である。

【0131】あるいは、別の実施態様において、上記のように2個または4個のパラメータではなく、1個のみのパラメータを使用して画素の不均一特性を表すことが出来る。すなわち、単一のパラメータを使用して画素の不均一特性を表すようにして更に単純化を行なう。

【0132】更に具体的には、多くの場合、画素ごとのゲイン係数Cの変動は小さく、Voffsetのみが不均一性の有意の原因として残る。これは、TFT相互コンダクタンスパラメータkと電圧ゲイン係数Bが均一のとき発生する。この場合、各画素のVoffsetのみを求めれば十分である。そうすると、データ補正は乗法を行なわず(ゲイン係数が均一であると見なされるので)、オフセットパラメータの加算のみを行なう。

【0133】この単一パラメータ手法は、上記のオートゼロ化OLED画素構造に類似である。この単一パラメータ補正方法は、コンピュータ費用を低減するとともに、満足すべきディスプレイ均一性を生み出すはずである。しかし、ディスプレイの均一性保持が非常に重要な特定のディスプレイの使用に於ては、コンピュータの複雑さと費用が増しても、上記の2個または4個パラメータ方法を使用することが出来る。

【0134】ここでも、単一パラメータ抽出とデータ補正に関して、ディスプレイ初期化プロセスはデータのフォーマット(形式)に左右される。単一パラメータ手法は、ビデオデータが、(1)画素電圧、(2)画素電流、および(3)ガンマ補正された画素輝度、を表す場合に、ディスプレイの初期化とビデオデータの補正に使用することが出来る。

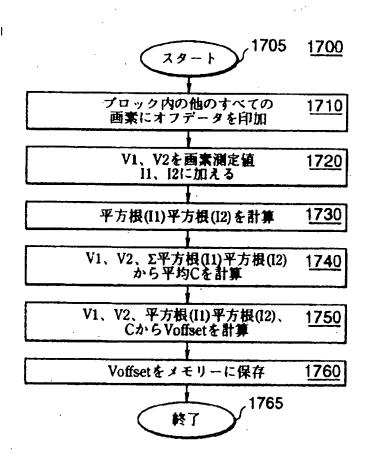

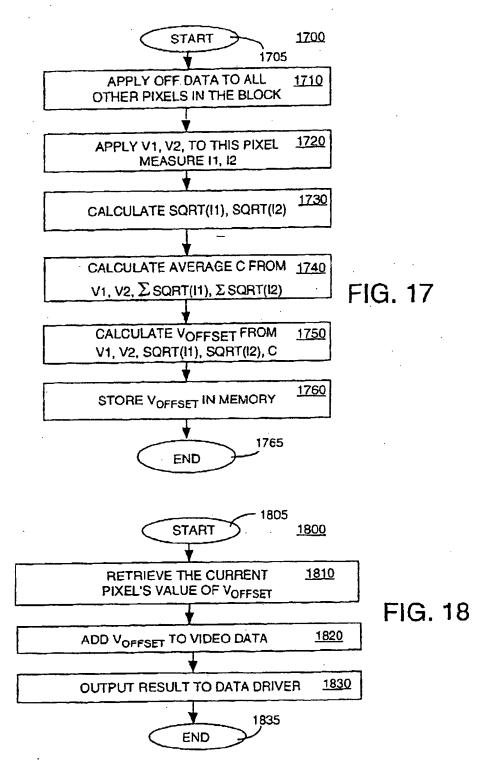

【0135】図17は、全画素のパラメータの測定によるディスプレイの初期化方法のフローチャートを示す。方法1700は、ステップ1705から始まってステップ1710へ進み、そこで、画素ブロック内の対象画素以外のすべての画素に「オフ」データ電圧が印加される。 ステップ1720において、対象とする特定の画素に関するVoffsetとCを求めるため、方法1700は、2個のデータ電圧(V1とV2)を印加し、各データ電圧ごとに電流を測定する。

【0136】ステップ1730において、電流I1とI2の平方根を計算する。好ましい実施態様において、この計算に平方根表を使用する。

【0137】Cの値は均一であると考えられるので、それは理想的には、ディスプレイ内の任意の場所で2点測定を行なうことによって、求め得ることに注目すべきである。しかしこれは、対象画素が異常であるかも知れないので、問題を有するかもしれない。従って、2点測定は、各画素ごとに行なわれる。

【0138】ステップ1740において、Cの平均値が

求められる。すなわち、各電流測定値に関する√Iを計算するための表を使用して、ディスプレイのCの平均値が計算できる。

【0139】ステップ1750において、各画素の電流 測定値から平均値Cを使用して、各画素のVoffsetが求 められる。このようにして、ディスプレイ全体にわたる Cの小変動がVoffsetの計算によって部分的に補正され る。上記理由により、各画素の電流の測定は、可能な最 高データ電圧において測定することが望ましい。

【0140】最後にステップ1760において、各画素 10のVoffsetが記憶装置、例えばメモリーに保存される。 次に、方法1700はステップ1765において終了する。

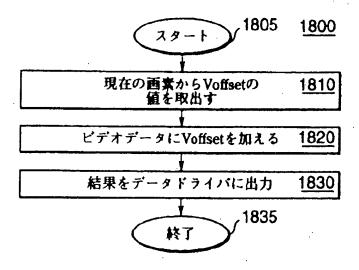

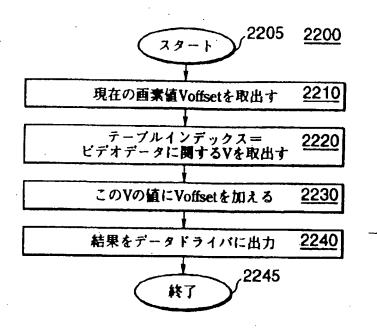

【0141】図18は、画素電圧を表す入力ビデオデータの補正方法1800のフローチャートである。方法1800は、ステップ1805から始まり、ステップ1810へ進み、そこで、対象画素に関して保存されているパラメータVoffsetを取り出す。

【0142】ステップ1820において、方法1800は、取出したパラメータVoffsetを使用して入力ビデオ 20データのキャリブレーションを行なう。より具体的には、保存されたVoffsetの値に基づいて、各画素に関するVdata = Voffset + Vdata の値を計算する。【0143】ステップ1830において、得られたVdata、すなわち補正された、または調整された入力データは画素アレイのデータドライバへ送られる。方法1800は次に、ステップ1835において終了する。

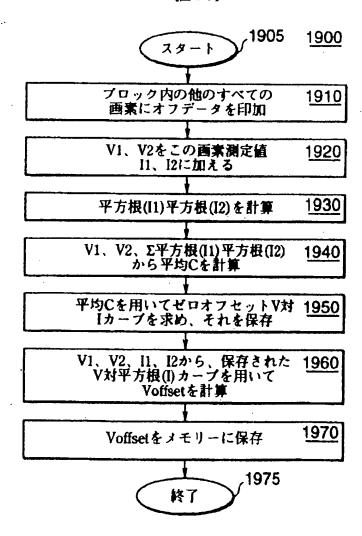

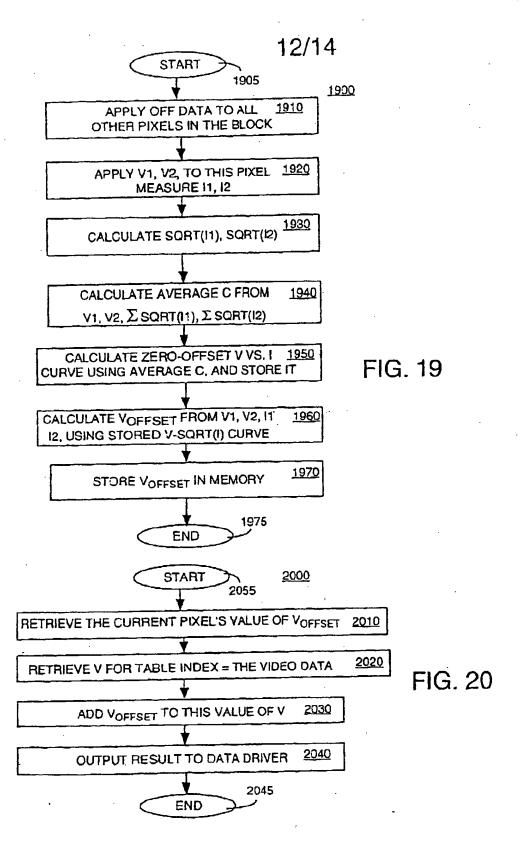

【0144】図19は、ビデオデータが画素電流を表す 状況に関する全画素のパラメータの測定によるディスプレイの初期化方法1900のフローチャートである。方 30 法1900は上記方法1700に酷似している。上記方 法1700との相違は、方法1900が追加のステップ 1950を取り入れて計算されたCの平均値を使用して、ゼロ・オフセットデータ電圧対画素電流の表を作成する場合である。この点から先の初期化とデータ補正プロセスにおいては、この表を使用することにより、平方根演算を行わない。この表は、平方根関数より高い精度で、画素の電流-電圧特性を表すものと期待される。この表は次に、後で使用するため、記憶装置、例えばメモリーに保存される。次に、個々の画素電流測定値を、この表に入れるためのインデックスとして使用して、個々の画素オフセットVoffsetを求める。

【0145】図20は、画素電流、すなわち輝度を表す 入力ビデオデータの補正方法2000のフローチャート\*

$$V_{data} = V_{off} + C(I)I$$

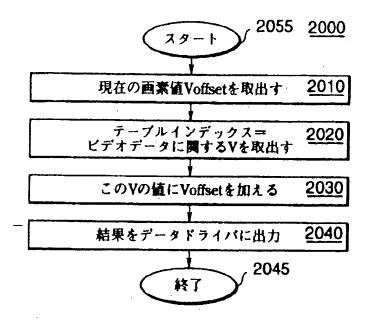

【0152】ここで、C(I)はIの弱い関数である。 ここでも、上記のように、オフセット項とゲイン係数の みを求めればよい程度に、電流が十分に高ければ、D<sup>■</sup> ✓ I 項をVorr項に含めることが出来る。しかし、オフ \*である。方法2000は、ステップ2005から始まり、ステップ2010へ進み、そこで現在対象とする画素のVoffserを記憶装置から取出す。

【0146】ステップ2020において、ゼロ・オフセットデータ電圧対画素電流の表を使用して入力ビデオデータ電流からゼロ・オフセットデータ電圧を求める。ステップ2030において、このゼロ・オフセットデータ電圧を、取出されたVoffsetに加える。最後に、ステップ2040において、補正または調整された入力ビデオデータを画素アレイのデータドライバへ送る。

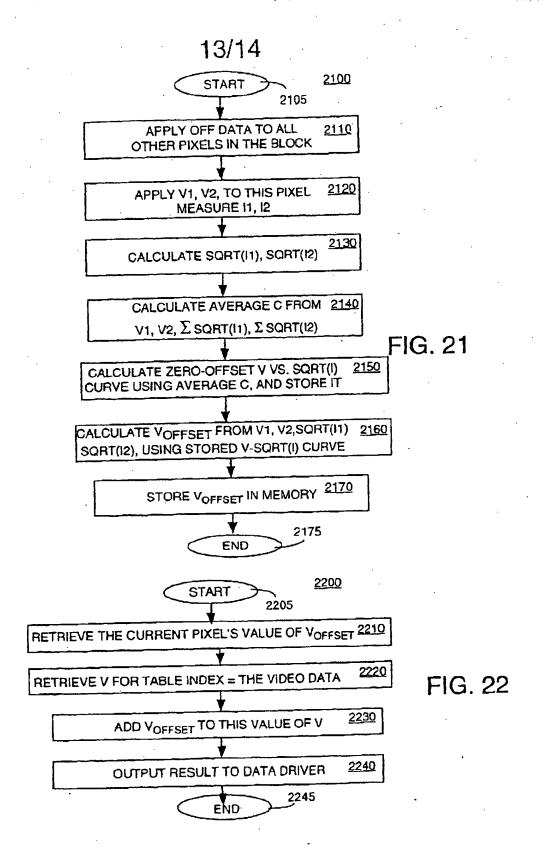

【0147】要するに、ビデオデータがディスプレイモ ジュールに導入されると、各電流に対応するゼロ・オフ セットデータ電圧がV-I表内で検索される。次に、保 存されている画素オフセットをゼロ・オフセット電圧に 加算し、その結果がデータドライバへの入力となる。方 法2000は次にステップ2045において終了する。 【0148】図21は、ビデオデータがガンマ補正され た輝度データを表す状況に関する全画素のパラメータの 測定によるディスプレイの初期化方法2100のフロー チャートである。方法2100は、上記方法1900に 酷似している。方法2100と上記方法1900との相 違は、ステップ2150において、計算されたCの平均 値を使用してゼロ・オフセットデータ電圧対画素電流の 平方根の表を作成するときである。すなわち、ビデオデ ータは、√Iを表すものとして近似させることが出来 る。従って、Cの平均値を使用してVdata対√Iのゼロ ・オフセット表を作成し、この表をメモリーなどの記憶 装置に保存する。

【0149】図22は、ガンマ補正された輝度データを表す入力ビデオデータの補正方法2200のフローチャートである。方法2200は、上記方法2000に酷似している。上記方法2000との相違は、Vdata対√Iのゼロ・オフセット表において発生する。従って、要するに、入ってくるビデオデータを使用してゼロ・オフセットデータ電圧を探し、保存された画素オフセットをこれらの電圧に加える。

【0150】上記説明において、OLED駆動トランジスタN2が飽和状態で作動するものと見なしている。N2がライン形領域で作動するならば、類似の補正方法を使用することが出来る。その場合、画素の電流電圧特性は以下の式(11)で表される。

[0151]

【数11】

$$+ D \sqrt[m]{I} \qquad (11)$$

セット電圧のみを不均一と見なす単一パラメータ近似は、ゲイン係数C(I)が不均一なOLEDパラメータAとmを含むので、上記の飽和の場合に関する単一パラメータ近似ほど精度がよいとは予想されない。従って、

N2かライン形領域で作動するならば、2個パラメータ 補正方法の方が単一パラメータ補正方法よりもはるかに 性能がよいと思われる。

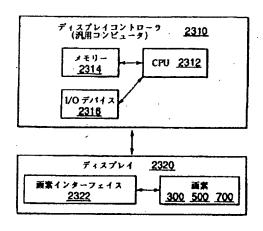

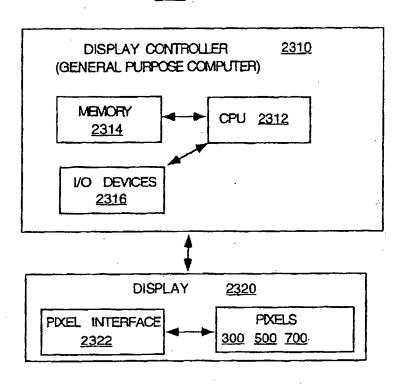

【0153】図23は、本発明の複数のアクティブマトリックスLED画素構造300、500、または700を備えたディスプレイ2320を使用したシステム2300のブロックダイヤグラムである。システム2300は、ディスプレイコントローラ2310とディスプレイ2320とから成る。

【0154】更に具体的には、ディスプレイコントロー 10 ラは、中央処理装置CPU(2312)、メモリー23 14、および複数のI/O装置(例えばマウス、キーボード、磁気装置や光装置などの記憶装置、モデム、A/Dコンバータ、上記の測定モジュール1330などの各種モジュール)を有する汎用コンピュータとすることが出来る。ディスプレイ2320を作動させるためのソフトウェア命令(例えば上記種々の方法)は、例えば記憶媒体からメモリー2314ヘロードし、CPU2312によって実行することが出来る。従って、本発明のソフトウェア命令は、コンピュータで読むことの出来る媒体 20に保存することが出来る。

【0155】ディスプレイ2320は、画素インターフェイス2322と、複数の画素(画素構造300、500、または700)とから成る。画素インターフェイス2322は画素300、500、または700の駆動に必要な回路を含む。例えば、画素インターフェイス2322は、図1に示したようなマトリックス・アドレッシング・インターフェイスとすることが出来、また、オプションとして追加の上記の信号ライン/制御ラインを含むことが出来る。

【0156】従って、システム2300は、ラップトップコンピュータとして実施することが出来る。あるいは、ディスプレイコントローラ2310は、マイクロコントローラとして、または特定用途の集積回路(ASIC)として、またはハードウェアとソフトウェア命令との組合せとして、実施することが出来る。要するに、システム2300は、本発明を組込んだ大きなシステム内において実施することが出来る。

【0157】本発明を、NMOSトランジスタを使用するものとして説明したが、本発明は、関連電圧が逆転したPMOSトランジスタを使用しても実現可能である。

【0158】以上、本発明の種々の実施態様を本明細書 に示しかつ詳細に説明したが、本発明の要旨を超えない 限りにおいて多くの態様を取り得ることが出来る。

[0159]

【発明の効果】本発明のディスプレイは輝度の均一性が 大幅に改善されており、その工業的価値は高い。

【図面の簡単な説明】

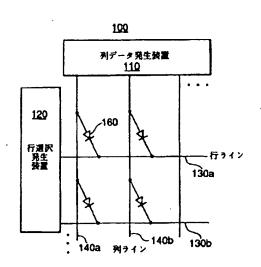

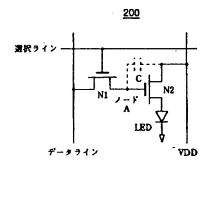

【図1】マトリックスアドレッシングインターフェイス のブロック図 【図2】従来技術のアクティブマトリックスLED画素 構造の略図

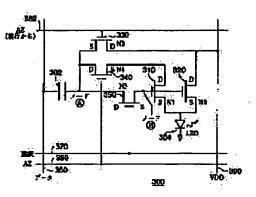

【図3】本発明のアクティブマトリックスLED画素構造の略図

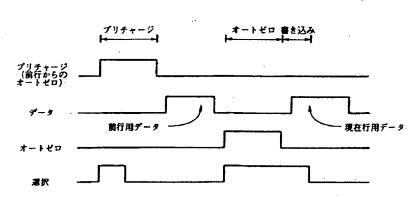

【図4】図3のアクティブマトリックスLED画素構造のためのタイミング図

【図5】本発明の代替実施態様のアクティブマトリックスLED画素構造の略図

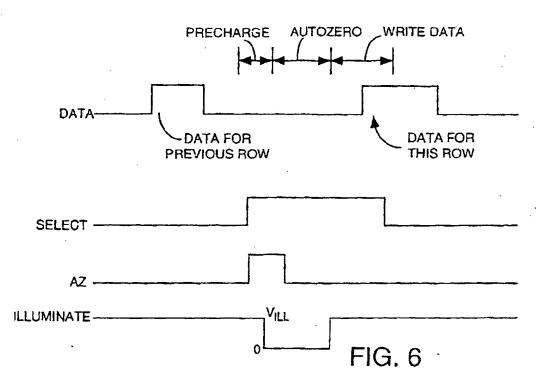

【図6】図5のアクティブマトリックスLED画素構造のためのタイミング図

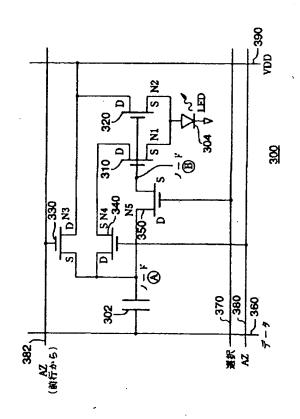

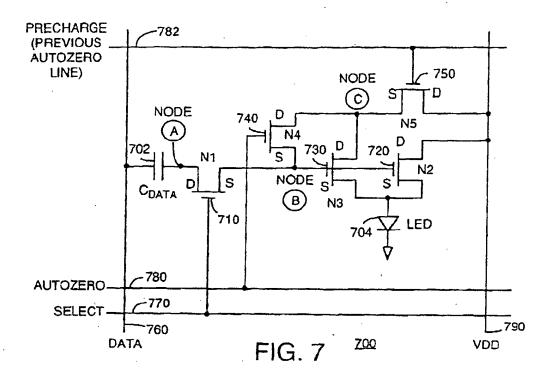

【図7】本発明の代替実施態様のアクティブマトリック スLED画素構造の略図

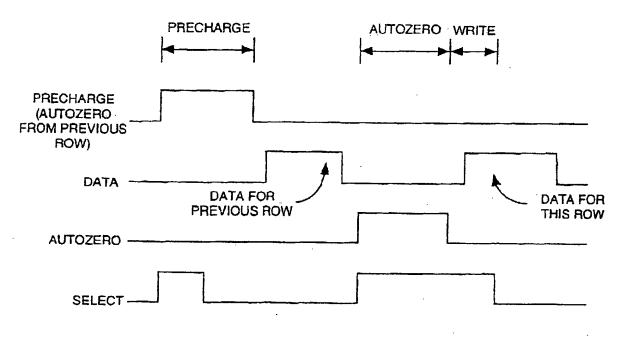

【図8】図7のアクティブマトリックスLED画素構造のためのタイミング図

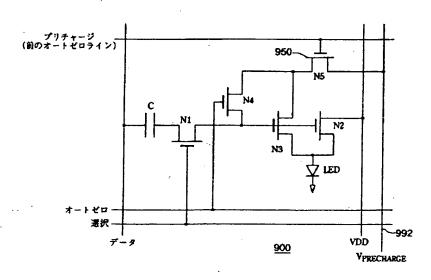

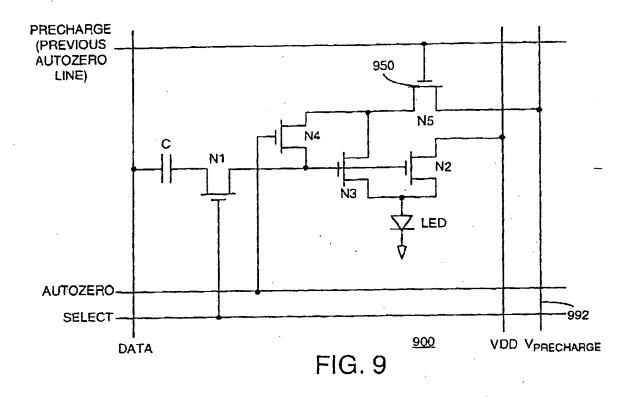

【図9】本発明の代替実施態様のアクティブマトリックスLED画素構造の略図

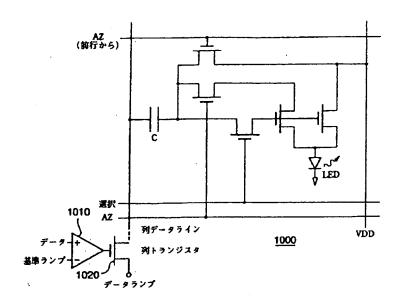

【図10】本発明の代替実施態様のアクティブマトリックスLED画素構造の略図

【図11】図10のアクティブマトリックスLED画素 構造のためのタイミング図

【図12】画素アレイを相互接続して画素ブロックとし た略図

【図13】ディスプレイとディスプレイコントローラと の相互接続の略図

【図14】全画素のパラメータの測定によってディスプレイを初期化する方法のフローチャート

【図15】画素電圧を表す入力データの補正方法のフローチャート

【図16】画素電流すなわち輝度を表す入力ビデオデー 30 タの補正方法のフローチャート

【図17】ビデオデータが画素電圧を表す場合、全画素 のパラメータの測定によってディスプレイを初期化する 方法のフローチャート

【図18】 画素電圧を表す入力ビデオデータの補正方法のフローチャート

【図19】ビデオデータが画素電流を表す場合、全画素 のパラメータの測定によってディスプレイを初期化する 方法のフローチャート

【図20】 画素電流すなわち輝度を表す入力ビデオデータの補正方法のフローチャート

【図21】ビデオデータがガンマ補正された輝度データを表す場合、全画素のパラメータの測定によってディスプレイを初期化する方法のフローチャート

【図22】ガンマ補正された輝度データで表された入力 ビデオデータの補正方法のフローチャート

【図23】本発明による複数のアクティブマトリックス LED画素構造を有するディスプレイを使用したシステ ムのブロック図

【符号の説明】

50 100: ディスプレイ

31 110:列データ発生装置 710:第1トランジスタ 120:行データ発生装置 720:第2トランジスタ 130:行ライン 730:第3トランジスタ 160:表示要素(画素). 740:第4トランジスタ 750:第5トランジスタ 200:従来技術のアクティブマトリックスLED画素 760: データライン 構造 300:本発明の画素構造 770:選択ライン 302:コンデンサ 780:オートゼロライン 304:LED (OLED) 782:前の行からのオートゼロライン (光要素) 10 790: VDDライン 310:第1トランジスタ 320:第2トランジスタ 900:本発明の好ましい画素構造 330:第3トランジスタ 992: Vprecharge 950:第5トランジスタ 340:第4トランジスタ 350:第5トランジスタ 1000:本発明の画素構造 360: データライン 1010:データドライバ 1020:列トランジスタ 370:選択ライン 380:オートゼロライン 1200:画素ブロック 382:前の行からのオートゼロライン 1210:検知ピン (VDD/SENSE) 1310:ディスプレイ -390: VDDライン 20 1320: ディスプレイコントローラ 500:本発明の好ましい画素構造 510:第1トランジスタ 1330:測定モジュール 1332:トランジスタP2 520:第2トランジスタ 530:第3トランジスタ 1334:電流検知回路 502:コンデンサ 1350: VDDコントロールモジュール 540:ショットキダイオード 1352:トランジスタP1 550:LED (OLED) (光要素) 2300:システム 2310:ディスプレイコントローラ 2312:中央処理装置CPU

570:選択ライン 560:データライン 580:オートゼロライン

590:点灯ライン

700:本発明の好ましい画素構造

702:コンデンサ

704:LED (OLED) (光要素)

【図1】

【図2】

2314:メモリー 30 2316:I/O装置

2320:ディスプレイ

2322: 画素インターフェイス

[図7]

【図23】

【図8】

【図9】

[図10]

【図11】

【図15】

【図13】

【図14】

【図16】

【図17】

【図18】

【図19】

#### 【図20】

[図21]

【図22】

#### フロントページの続き

(51) Int. Cl. 6

識別記号

H01L 33/00

(72)発明者 ジェームズ ハロルド アサトン アメリカ合衆国、ニュージャージー州・ 08551、リンゴーズ、エヴェリットス ロ ード 45 FΙ

HO1L 33/00

J

(72)発明者 ロジャー グリーン スチュアート アメリカ合衆国、ニュージャージー州・ 08853、ネシャニック ステーション、ス キー ドライブ 3

(72)発明者 フランク パウル キュオモ アメリカ合衆国、ニュージャージー州・ 08540、プリンストン、リーヴィット レ ーン 74 【外国語明細書】

15

# ACTIVE MATRIX LIGHT EMITTING DIODE PIXEL STRUCTURE AND CONCOMITANT METHOD

This application claims the benefit of U.S. Provisional Application

No. 60/060, 386 filed September 29, 1997, and U.S. Provisional Application

No. 60/060, 387 filed September 29, 1997, which are herein incorporated by reference.

The invention relates to an active matrix light emitting diode pixel structure. More particularly, the invention relates to a pixel structure that improves brightness uniformity by reducing current nonuniformities in a light-emitting diode of the pixel structure and method of operating said active matrix light emitting diode pixel structure.

#### BACKGROUND OF THE DISCLOSURE

Matrix displays are well known in the art, where pixels are illuminated using matrix addressing as illustrated in FIG. 1. A typical display 100 comprises a plurality of picture or display elements (pixels) 160 that are arranged in rows and columns. The display incorporates a column data generator 110 and a row select generator 120. In operation, each row is sequentially activated via row line 130, where the corresponding pixels are activated using the corresponding column lines 140. In a passive matrix display, each row of pixels is illuminated sequentially one by one, whereas in an active matrix display, each row of pixels is first loaded with data sequentially. Namely, each row in the passive matrix display is only "active" for a fraction of the total frame time, whereas each row in the active matrix display can be set to be "active" for the entire total frame time.

With the proliferation in the use of portable displays, e.g., in a laptop computer, various display technologies have been employed, e.g., liquid crystal display (LCD) and light-emitting diode (LED) display. Generally, an important criticality in portable displays is the ability to conserve power,

thereby extending the "on time" of a portable system that employs such display.

In a LCD, a backlight is on for the entire duration in which the display is in use. Namely, all pixels in a LCD are illuminated, where a "dark" pixel is achieved by causing a polarized layer to block the illumination through that pixel. In contrast, a LED display only illuminates those pixels that are activated, thereby conserving power by not having to illuminate dark pixels.

FIG. 2 illustrates a prior art active matrix LED pixel structure 200

10 having two NMOS transistors N1 and N2. In such pixel structure, the data

(a voltage) is initially stored in the capacitor C by activating transistor N1

and then activating "drive transistor" N2 to illuminate the LED. Although

a display that employs the pixel structure 200 can reduce power

consumption, such pixel structure exhibits nonuniformity in intensity level

15 arising from several sources.

First, it has been observed that the brightness of the LED is proportional to the current passing through the LED. With use, the threshold voltage of the "drive transistor" N2 may drift, thereby causing a change in the current passing through the LED. This varying current contributes to the nonuniformity in the intensity of the display.

Second, another contribution to the nonuniformity in intensity of the display can be found in the manufacturing of the "drive transistor" N2. In some cases, the "drive transistor" N2 is manufactured from a material that is difficult to ensure initial threshold voltage uniformity of the transistors such that variations exist from pixel to pixel.

Third, LED electrical parameters may also exhibit nonuniformity. For example, it is expected that OLED (organic light-emitting diode) turn-on voltages may increase under bias-temperature stress conditions.

Therefore, a need exists in the art for a pixel structure and concomitant method that reduces current nonuniformities due to threshold voltage variations in a "drive transistor" of the pixel structure.

#### SUMMARY OF THE INVENTION

The present invention incorporates a LED (or an OLED) pixel structure and method that improve brightness uniformity by reducing current nonuniformities in a light-emitting diode of the pixel structure. In one embodiment, a pixel structure having five transistors is disclosed. In an alternate embodiment, a pixel structure having three transistors and a diode is disclosed. In yet another alternate embodiment, a different pixel structure having five transistors is disclosed. In yet another alternate embodiment, an additional line is provided to extend the autozeroing voltage range. Finally, an external measuring module and various external measuring methods are disclosed to measure pixel parameters that are then used to adjust input pixel data.

#### BRIEF DESCRIPTION OF THE DRAWINGS

- The teachings of the present invention can be readily understood by considering the following detailed description in conjunction with the accompanying drawings, in which:

- FIG. 1 depicts a block diagram of a matrix addressing interface;

- FIG. 2 depicts a schematic diagram of a prior art active matrix LED 20 pixel structure:

- FIG. 3 depicts a schematic diagram of an active matrix LED pixel structure of the present invention;

- FIG. 4 depicts a timing diagram for active matrix LED pixel structure of FIG. 3;

- FIG. 5 depicts a schematic diagram of an alternate embodiment of an active matrix LED pixel structure of the present invention;

- FIG. 6 depicts a timing diagram for active matrix LED pixel structure of FIG. 5;

- FIG. 7 depicts a schematic diagram of an alternate embodiment of an active matrix LED pixel structure of the present invention;

- FIG. 8 depicts a timing diagram for active matrix LED pixel structure of FIG. 7;

- FIG. 9 depicts a schematic diagram of an alternate embodiment of an active matrix LED pixel structure of the present invention;

- FIG. 10 depicts a schematic diagram of an alternate embodiment of an active matrix LED pixel structure of the present invention;

- FIG. 11 depicts a timing diagram for active matrix LED pixel structure of FIG. 10;

- FIG. 12 illustrates a schematic diagram of an array of pixels interconnected into a pixel block;

- FIG. 13 is a schematic diagram illustrating the interconnection between a display and a display controller;

- FIG. 14 illustrates a flowchart of a method for initializing the display by measuring the parameters of all the pixels;

- FIG. 15 illustrates a flowchart of a method for correcting input data representing pixel voltages;

- FIG. 16 illustrates a flowchart of a method for correcting input video data representing pixel currents, i.e., luminances;

- FIG. 17 illustrates a flowchart of a method for initializing the display by measuring the parameters of all the pixels where the video data represent pixel voltage;

- FIG. 18 illustrates a flowchart of a method for correcting input video data representing pixel voltages;

- FIG. 19 illustrates a flowchart of a method for initializing the display by measuring the parameters of all the pixels for the situation where the video data represents pixel currents;

- FIG. 20 illustrates a flowchart of a method for correcting input video data represented in pixel currents, i.e., luminances;

- FIG. 21 illustrates a flowchart of a method for initializing the display by measuring the parameters of all the pixels for the situation where the video data represents gamma-corrected luminance data;

- FIG. 22 illustrates a flowchart of a method for correcting input video data represented in gamma-corrected luminance data; and

FIG. 23 depicts a block diagram of a system employing a display having a plurality of active matrix LED pixel structures of the present invention.

To facilitate understanding, identical reference numerals have been used, where possible, to designate identical elements that are common to the figures.

#### DETAILED DESCRIPTION

FIG. 3 depicts a schematic diagram of an active matrix LED pixel structure 300 of the present invention. In the preferred embodiment, the active matrix LED pixel structure is implemented using thin film

5 transistors (TFTs), e.g., transistors manufactured using poly-silicon or amorphous silicon. Similarly, in the preferred embodiment, the active matrix LED pixel structure incorporates an organic light-emitting diode (OLED). Although the present pixel structure is implemented using thin film transistors and an organic light-emitting diode, it should be understood that the present invention can be implemented using other types of transistors and light emitting diodes.

The present pixel structure 300 provides a uniform current drive in the presence of a large transistor threshold voltage (V<sub>t</sub>) nonuniformity and OLED turn-on voltage nonuniformity. In other words, it is desirable to maintain a uniform current through the OLEDs, thereby ensuring uniformity in the intensity of the display.

Referring to FIG. 3, pixel structure 300 comprises five NMOS transistors N1 (310), N2 (320), N3 (330), N4 (340) and N5 (350), a capacitor 302 and a LED (OLED) (light element) 304 (light element). A Select line 370 is coupled to the gate of transistor 350. A Data line 360 is coupled to one terminal of the capacitor 302. An Autozero line 380 is coupled to the gate of transistor 340. A VDD line 390 is coupled to the drain of transistors 320 and 330. An Autozero line 382 from a previous row in the pixel array is coupled to the gate of transistor 330.

It should be noted that Autozero line 382 from a previous row can be implemented as a second Select line. Namely, the timing of the present pixel is such that the Autozero line 382 from a previous row can be exploited without the need of a second Select line, thereby reducing complexity and cost of the present pixel.

One terminal of the capacitor 302 is coupled (at node A) to the source of transistor 330 and to the drain of transistors 340 and 350. The source of

transistor 350 is coupled (at node B) to the gate of transistors 310 and 320. The drain of transistor 310 is coupled to the source of transistor 340. Finally, the source of transistors 310 and 320 are coupled to one terminal of the LED 304.

As discussed above, driving an organic LED display is challenging in light of the various nonuniformities. The present invention is an architecture for an organic LED display that addresses these criticalities. Namely, each LED pixel is driven in a manner that is insensitive to variations in the LED turn-on voltage, as well as to variations in the TFT threshold voltages. Namely, the present pixel is able to determine an offset voltage parameter using an autozeroing method that is used to account for these variations in the LED turn-on voltage, and the TFT threshold voltages.

Furthermore, data is provided to each pixel as a data voltage in a

15 manner that is very similar to that used in conventional active-matrix

liquid crystal displays. As a result, the present display architecture can be

employed with conventional column and row scanners, either external or

integrated on the display plate.

The present pixel uses five (5) TFTs and one capacitor, and the LED.

20 It should be noted that TFTs are connected to the anode of the LED, and not the cathode, which is required by the fact that ITO is the hole emitter in conventional organic LED. Thus, the LED is coupled to the source of a TFT, and not the drain. Each display column has 2 row lines (the auto-zero line and the select line), and 1 1/2 column lines (the data line and the +Vdd line, which is shared by neighboring columns). The waveforms on each line are also shown in FIG. 4. The operation of the pixel 300 is described below in three phases or stages.

The first phase is a precharge phase. A positive pulse on the autozero (AZ) line of the previous row 382 turns "on" transistor 330 and

precharges node A of the pixel up to Vdd, e.g., +10 volts. Then the Data line

changes from its baseline value to write data into the pixel of the previous

row, and returns to its baseline. This has no net effect on the pixel under consideration.

The second phase is an auto-zero phase. The AZ and SELECT lines for the present row go high, turning "on" transistors 340 and 350 and

5 causing the gate of transistor N1 310 to drop, self-biasing to a turn-on voltage that permits a very small trickle of current to flow through the LED. In this phase the sum of the turn-on voltage of the LED and the threshold voltage of N1 are stored on the gate of N1. Since N1 and N2 can be placed very close together, their initial threshold voltages will be very similar. In addition, these two transistors should have the same gate to source voltage, Vgs. Since a TFT threshold drift depends only on Vgs over the life of the TFT, it can be assumed that the threshold voltages of these devices will track over the life of the TFT. Therefore, the threshold voltage of N2 is also stored on its gate. After auto-zeroing is complete, the Autozero line returns low, while Select line stays high.

The third phase is a data writing phase. The data is applied as a voltage above the baseline voltage on the Data line, and is written into the pixel through the capacitor. Then, the Select line returns low, and the sum of the data voltage, plus the LED turn-on voltage, plus N2's threshold voltage, is stored at node B for the rest of the frame. It should be noted that a capacitor from node B to +Vdd can be employed in order to protect the stored voltage from leaking away.

In sum, during the auto-zero phase, the LED's turn-on voltage, as well as N2's threshold voltage, are "measured" and stored at node B using a trickle current. This auto-zero phase is essentially a current-drive mode of operation, where the drive current is very small. It is only after the auto-zero phase, in the writing phase, that the voltage on the LED is incremented above turn-on using the applied data voltage. Thus, the present invention can be referred to as having a "hybrid drive," rather than a voltage drive or current drive. The hybrid drive method combines the advantages of voltage drive and current drive, without the disadvantages of either. Variations in the turn-on voltage of the LED and the threshold

voltage of the TFT are corrected, just as in current drive. At the same time, all lines on the display are driven by voltages, and can therefore be driven fast.

It should be noted that the data voltage increment applied to the 5 Data line 360 does not appear directly across the LED 304, but is split between Vgs of N2 320 and the LED. This simply means that there is a nonlinear mapping from the data voltage to the LED voltage. This mapping, combined with the nonlinear mapping from LED voltage to LED current, yields the overall transfer function from data voltage to LED 10 current, which is monotonic, and, as noted above, is stable over the life of the display.

An advantage of the present pixel architecture 300 is that the transistors in the pixel whose threshold shifts are uncorrected (N3, N4, and N5) are turned on for only one row-time per frame, and therefore have a 15 very low duty-cycle and are not expected to shift appreciably. Additionally, N2 is the only transistor in the LED's current path. Additional transistors connected in series on this path may degrade display efficiency or may create problems due to uncorrected TFT threshold shifts, and, if shared by all pixels on a column, may introduce significant vertical crosstalk.

Select and Autozero (AZ) pulses are generated by row scanners. The column data is applied on top of a fixed (and arbitrary) baseline voltage in the time-slot between AZ pulses. The falling edge of Select signal occurs while data is valid on the Data line. Various external and integrated column-scanner designs, either of the direct-sample or chopped-ramp type, 25 can produce data with this timing.

20

The above pixel architecture permits large direct-view displays to be built using organic LEDs. Of course, the present pixel structure is also applicable to any display technology that uses display elements requiring drive current, particularly, when the display elements or the TFTs have turn-on voltages that shift or are nonuniform.

FIG. 5 depicts a schematic diagram of an alternate embodiment of an active matrix LED pixel structure 500 of the present invention. The pixel

structure 500 is similar to the pixel structure 300 of FIG. 3, where a Schottky diode is now employed in lieu in of two transistors.

One potential disadvantage of the pixel structure 300 is the use of five transistors per pixel. Namely, using so many transistors in each pixel may impact the pixel's fill-factor (assuming bottom-side emission through the active plate), and also its yield. As such, the pixel structure 300 employs a single Schottky diode in each pixel that reduces the number of transistors from five to three transistors, while performing the same functions as previously described.

10 Referring to FIG. 5, pixel structure 500 comprises three NMOS transistors N1 (510), N2 (520), N3 (530), a capacitor 502, a Schottky diode 540 and a LED (OLED) 550 (light element). A Select line 570 is coupled to the gate of transistor 530. A Data line 560 is coupled to one terminal of the capacitor 502. An Autozero line 580 is coupled to the gate of transistor 520.

15 An Illuminate (similar to a VDD line) line 590 is coupled to one terminal of the Schottky diode 540.

One terminal of the capacitor 502 is coupled (at node A) to the drain of transistors 520 and 530. The source of transistor 530 is coupled (at node B) to the gate of transistor 510. The drain of transistor 510 is coupled to the source of transistor 520, and one terminal of the Schottky diode 540.

The pixel structure 500 also has three phases of operation: a precharge phase, an autozero phase, and a data writing phase as discussed below. All of the Illuminate lines are connected together at the periphery of the display, and before the precharge phase begins, the Illuminate lines are held at a positive voltage  $V_{\rm LL}$ , which is approximately +15V. For the purpose of the following discussion, a row under consideration is referred to as "row i". The waveforms on each line are also shown in FIG. 6.

The first phase is a precharge phase. Precharge is initiated when the Autozero (AZ) line turns on transistor N2, and the Select line turns on transistor N3. This phase is performed while the Data line is at a reset level. The voltage at Nodes A and B rises to the same voltage as the drain of transistor N1, which is a diode drop below V<sub>n1</sub>.

The second phase is an autozero phase. Next, the Illuminate line drops to ground. During this phase, all pixels on the array will briefly darken. Autozeroing of N1 now begins with the Schottky diode 540 causing the drain of transistor N1 to be isolated from the grounded Illuminate line.

When Node B has reached a voltage approximately equal to the threshold voltage of the transistor N1 plus the turn-on voltage of the LED 550, the AZ line is used to turn transistor N2 "off", and the Illuminate line is restored to V<sub>al</sub>. All pixels in unselected rows light up again.

The third phase is a data writing phase. Next, the data for row i is loaded onto the data line. The voltage rise at Nodes A and B will equal the difference between the Data line's reset voltage level and the data voltage level. Thus, variations in the threshold voltage of transistor N1 and the LED's turn-on voltage will be compensated. After the voltage at Node B has settled, the Select line for row i is used to turn off transistor N3, and the Data line is reset. The proper data voltage is now stored on the pixel until the next frame.

Thus, a three-transistor pixel for OLED displays has been described, that possesses the advantages described previously for the 5-transistor pixel 300, but requires fewer transistors. An additional advantage is that the 5-transistor pixel employs separate transistors for autozeroing and driving the LED. Proper operation of pixel 300 requires that these two transistors have matching initial thresholds that would drift over life in the same way. Recent experimental data suggest that TFTs with different drain voltages (as these two transistors have) may not drift in the same way. Thus, pixel 500 performs autozeroing on the same transistor that drives the LED, such that proper autozeroing is guaranteed.

FIG. 7 depicts a schematic diagram of an alternate embodiment of an active matrix LED pixel structure 700 of the present invention. The pixel structure 700 is similar to the pixel structure 300 of FIG. 3, with the

30 exception that pixel structure 700 may generate a more precise autozero voltage.

Namely, referring to FIG. 3, the autozeroing arises from the fact that each precharge cycle, as shown in FIG. 3, injects a large positive charge  $Q_{\rm pc}$  onto Node A of the pixel 300. During the precharge phase, nearly all of the capacitance on Node A is from capacitor  $C_{\rm data}$ , such that the charge injected onto Node A is:

$$Q_{PC} \equiv C_{data} (V_{DO} - V_{A}) \tag{1}$$

where V<sub>A</sub> is the voltage that was on Node A before the precharge phase began. V<sub>A</sub> depends on the threshold voltage of N3 330 and the turn-on voltage of the LED 304, as well as the previous data applied to the pixel 300. Since C<sub>data</sub> is a large capacitance (approx. 1 pF), Q<sub>PC</sub> is also relatively large, on the order of ten picocoulombs.

When the pixel 300 is at a stable autozero level, Q<sub>pc</sub> flows through N1 310 and the LED 304 during the autozero phase. Since the autozero interval is short (approximately 10 µsec.), N1 may be left with a gate-to-source autozero voltage higher than its threshold voltage, and similarly the LED autozeroes above its turn-on voltage. Thus, the autozeroing process may not produce a true zero-current autozero voltage at Nodes A and B, but instead, an approximation of a zero-current autozero voltage.

It should be noted that it is not necessary to produce a true zero-current autozero voltage, corresponding to exactly zero current through N1 and the LED. The desirable goal is to obtain an autozero voltage that permits a small trickle of current (approximately ten nanoamps) to flow through N1 310 and the LED 304. Since the autozero interval is approximately 10 µsec, then  $Q_{\rm PC}$  should be on the order of 0.1 picocoulomb. As noted above,  $Q_{\rm PC}$  is approximately 10 picocoulombs.

The effect of such a large  $Q_{\rm rc}$  is that the pixel's stable autozero voltage may well be above the sum of the threshold and turn-on voltages. This condition by itself is not a problem, if the excess autozero voltages were

uniform across the display. Namely, the effect can be addressed by offsetting all the data voltages accordingly.

However, a potential difficulty may arise if Q<sub>PC</sub> is not only large, but also depends on the previous data voltage, and on the autozero voltage itself. If this condition develops in the display, then not only will all pixels have large excess autozero voltages, but also the magnitude of the excess voltage may vary from pixel to pixel. In effect, the autozeroing of pixel 300 may not produce a uniform display under such a condition.

To address this criticality, the pixel structure 700 is capable of reducing the precharge  $Q_{rc}$  to a very small value. Additionally, a "variable precharge" method is disclosed, that permits  $Q_{rc}$  to vary, depending on the amount of charge that is actually needed for autozeroing. In brief, if the current autozero voltage is too low,  $Q_{rc}$  assumes its maximum value of about 0.1 picocoulomb in order to raise the autozero voltage toward its desired value. However, if the current autozero voltage is too high, then  $Q_{rc}$  is essentially zero, allowing the autozero voltage to drop quickly.

Referring to FIG. 7, pixel structure 700 comprises five NMOS transistors N1 (710), N2 (720), N3 (730), N4 (740), N5 (750), a capacitor 702, and a LED (OLED) 704 (light element). A Select line 770 is coupled to the gate of transistor 710. A Data line 760 is coupled to one terminal of the capacitor 702. An Autozero line 780 is coupled to the gate of transistor 740. A VDD line 790 is coupled to the drain of transistors 720 and 750. An Autozero line 782 from a previous row in the pixel array is coupled to the gate of transistor 750.

It should be noted that Autozero line 782 from a previous row can be implemented as a second Select line. Namely, the timing of the present pixel is such that the Autozero line 782 from a previous row can be exploited without the need of a second Select line, thereby reducing complexity and cost of the present pixel.

One terminal of the capacitor 702 is coupled (at node A) to the drain of transistor 710. The source of transistor 710 is coupled (at node B) to the gate of transistors 720 and 730 and is coupled to the source of transistor

740. The drain of transistor 740 is coupled (at node C) to the source of transistor 750, and to the drain of transistor 730. Finally, the source of transistors 730 and 720 are coupled to one terminal of the LED 704.

More specifically, the pixel 700 is similar to the pixel 300, except that the precharge voltage is now applied to Node C, which is the drain of transistor N3 730. In addition, there are also some timing changes as shown in FIG. 8. The operation of the pixel 700 is again described below in three phases or stages.

The first phase is a precharge phase that occurs during the previous line time, i.e., before data is applied to the previous row's pixels. A positive pulse on the Select line turns "on" N1, thereby shorting Nodes A and B together, which returns the pixel 700 to the state it was in after the last autozero phase. Namely, the pixel is returned to a data-independent voltage that is the pixel's most recent estimate of its proper autozero voltage. While transistor N1 is "on", a positive pulse on the Autozero line 782 from a previous row line turns "on" transistor N5, thereby precharging Node C to V<sub>44</sub>. In turn, transistors N1 and N5 are turned "off".

The relative timing of turning transistors N1 and N5 "on" and "off" is not very important, except that transistor n1 must be "on" before transistor N5 is turned "off". Otherwise, transistor N3 may still be turned "on" in response to the old data voltage, and the charge injected onto Node C may inadvertently drain away through transistor N3.

After the precharge phase, the charge  $Q_{\rm pc}$  is stored at Node C on the gate-to-source/drain capacitances of transistors N3, N4 and N5. Since these capacitances add up to a very small capacitance (about 10 fF), and the precharge interval raises Node C about 10 V,  $Q_{\rm pc}$  is initially approximately 0.1 picocoulombs. However, this charge will drain from Node C to varying degrees prior to the autozero phase, depending on how well the previous autozero voltage approximates the true autozero voltage. Thus, it is more accurate to indicate that  $Q_{\rm pc} \leq 0.1$  picocoulomb, depending on how much charge is needed for autozeroing. This is the variable precharge feature. If the last autozero voltage is too low, N3 is nonconducting after the precharge

phase, and  $Q_{\rm PC}$  should stay at its maximum value, raising the autozero voltage toward its desired level during the autozero phase. If the last autozero voltage is too high, N3 is conducting, and  $Q_{\rm PC}$  will drain off by the time the autozero phase occurs, allowing the autozero voltage to drop quickly.

Although the relative timing for transistors N1 and N5 is not critical, the preferred timing is shown in FIG. 8. The two transistors N1 and N5 turn "on" at the same time in order to minimize the time required for precharge. N1 turns "off" before N5 such that the (intentional) draining of  $Q_{\rm PC}$  from Node C is in response to a Node B voltage that has been capacitively pushed down by N1 turning "off". This ensures that the draining of  $Q_{\rm PC}$  from Node C is in response to a Node B voltage that is the same as when zero data is applied to the pixel.

In sum, the pixel 700 when compared to the pixel 300, provides a

15 means of precharging the pixel that allows a more effective autozeroing.

Specifically, the autozeroing of pixel 700 is more accurate, faster, and data independent. Computer simulations have verified that the pixel 700 autozeroes well and is able to maintain a nearly constant OLED current vs. data voltage characteristic over an operational lifetime of 10,000 hours.

FIG. 9 depicts a schematic diagram of an alternate embodiment of an active matrix LED pixel structure 900 of the present invention. The pixel structure 900 is similar to the pixel structure 700 of FIG. 7, with the exception of having an additional V<sub>prechurge</sub> line 992, that permits the range of autozero voltages to be extended without raising the LED supply voltage

25 V<sub>st</sub>. This additional modification of the pixel extends the life and efficiency of the pixel.

It should be noted that the above described pixels (200, 300, 700) have the limitation that the autozero voltage cannot exceed  $V_{dd}$ , since this is the precharge voltage. However, as the threshold voltages of transistors N2 and N3 drift over the life of the transistor, a point is reached where an autozero voltage higher than  $V_{dd}$  is required in order to compensate for drift in the TFT threshold voltage and in the OLED turn-on voltage. Since the

autozero voltage cannot reach higher voltages, display uniformity will quickly degrade, signaling the end of the useful life of the display. Raising  $V_{4d}$  will permit higher autozero voltages to be achieved, but at the expense of power efficiency, since  $V_{4d}$  is also the OLED drive supply.

Furthermore, the range of autozero voltages will be restricted even further if, in order to improve power efficiency,  $V_{\rm sd}$  is reduced to operate transistor N2 in the linear region. (Of course, this will require N2 to be made larger than if it was operated in saturation.) In this case, the operating lifetime will be quite short, since after a short period of operation, the autozero voltage will need to reach a level higher than  $V_{\rm sd}$ .

Referring to FIG. 9, an optional modification is incorporated into the pixel 700 that removes restrictions on the autozero voltage, thereby permitting it to be extended to well above V<sub>44</sub>. The pixel 900 is identical to the pixel 700 with the exception of an additional column line 992, that is coupled to the drain of transistor 950.

The column line 992 is added to the array to carry a DC voltage  $V_{precharge}$  to all the pixels. All of these column lines are connected together at the edge of the display. By raising  $V_{precharge}$  to a level higher than  $V_{dd}$ , the pixel 900 can precharge and autozero to a voltage higher than  $V_{cd}$ . A high value of  $V_{precharge}$  will have very little effect on display efficiency.

It should be noted that each  $V_{\text{precharge}}$  line 992 can be shared by neighboring columns of pixels. The  $V_{\text{precharge}}$  lines can also run as row lines, shared by neighboring rows.

In sum, a modification of the above OLED pixels is disclosed where an additional voltage line is provided to extend the range of the autozero voltages beyond V<sub>d</sub>. This allows the OLED drive transistor to operate at as low a voltage as needed for power efficiency, possibly even in the linear region, without restricting the range of autozero voltages. Thus, long operating lifetime and high efficiency can be obtained. Finally, although the present modification is described with respect to pixel 700, it should be understood that this optional modification can be employed with other

autozeroing pixel structures, including but not limited to, pixels 200 and 300 as discussed above.

Although the above pixel structures are designed for an OLED display in such a manner that transistor threshold voltage variations and OLED turn-on voltage variations in the pixel can be compensated, these pixel structures are not designed to address nonuniformity that is generated external to the pixel. It was pointed out that the pixel could be used with conventional column driver circuits, either external to the display plate or integrated on the display.

10 Unfortunately, integrated data drivers are typically not as accurate as external drivers. While commercially available external drivers can achieve ±12 mV accuracy, it has proven difficult to achieve accuracy better than ±50 mV using integrated drivers. The particular type of error produced by integrated drivers is primarily offset error, i.e., it is a data-15 independent DC level that adds to all data voltages. The offset error is nonuniform, i.e., the value of the DC level varies from one data driver to the next. Liquid crystal displays tend to be forgiving of offset errors because the liquid crystal is driven with opposite polarity data in successive frames, such that in one frame the offset error causes the liquid crystal to be slightly too dark, and in the next frame too light, but the average is nearly correct and the alternating errors are not noticeable to the eye. However, an OLED pixel is driven with unipolar data. Therefore, the bipolar cancellation of offset errors does not occur, and serious nonuniformity problems may result when integrated scanners are used.

FIG. 10 depicts a schematic diagram of an active matrix LED pixel structure 300 of the present invention coupled to a data driver 1010 via a column transistor 1020. The present invention describes a method for canceling offset errors in integrated data scanners for OLED displays.

Namely, the present method is designed to operate with any pixel in which the pixel is capacitively coupled to a data line, and has an autozero phase, e.g., pixels 200, 300, 500, and 700 as discussed above.

Referring to FIG. 10, the pixel 300 as described above is coupled to a Data line that provides the pixel with an analog level to establish the brightness of the OLED element. In FIG. 10, the Data line is driven by a data driver that uses the chopped ramp technique to set the voltage on the Data line. Various sources of error exist in this approach that may give rise to offset errors on the Data line. For example, the time at which the voltage comparator switches can vary depending on the comparator's maximum slew rate. It has also been observed experimentally that the maximum slew rate can be highly variable. The offset error will affect the voltage stored in the pixel. Since it is nonuniform, the offset error will also lead to brightness variations across the display.